## ACHARYA INSTITUTE OF TECHNOLOGY,

Bangalore

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

**NOTES FOR**

### "BASIC ELECTRONICS"

### (18ELN14/24)

MAMATHA S V Assistant Professor Dept .of ECE

## SEMICONDUCTOR DIDDES AND

#### APPLICATIONS.

Introduction: The term diode indentifies a two-electeode of two terminal device. & A Diode is a two-layer (PN junction) device which factificates conduction in One direction and blocks conduction in other direction. Diode affers a low resistance when folward brased and behaves as a open che when geweise brased. A constant voltage drop occurs across the diode when itte diode is folward brased.

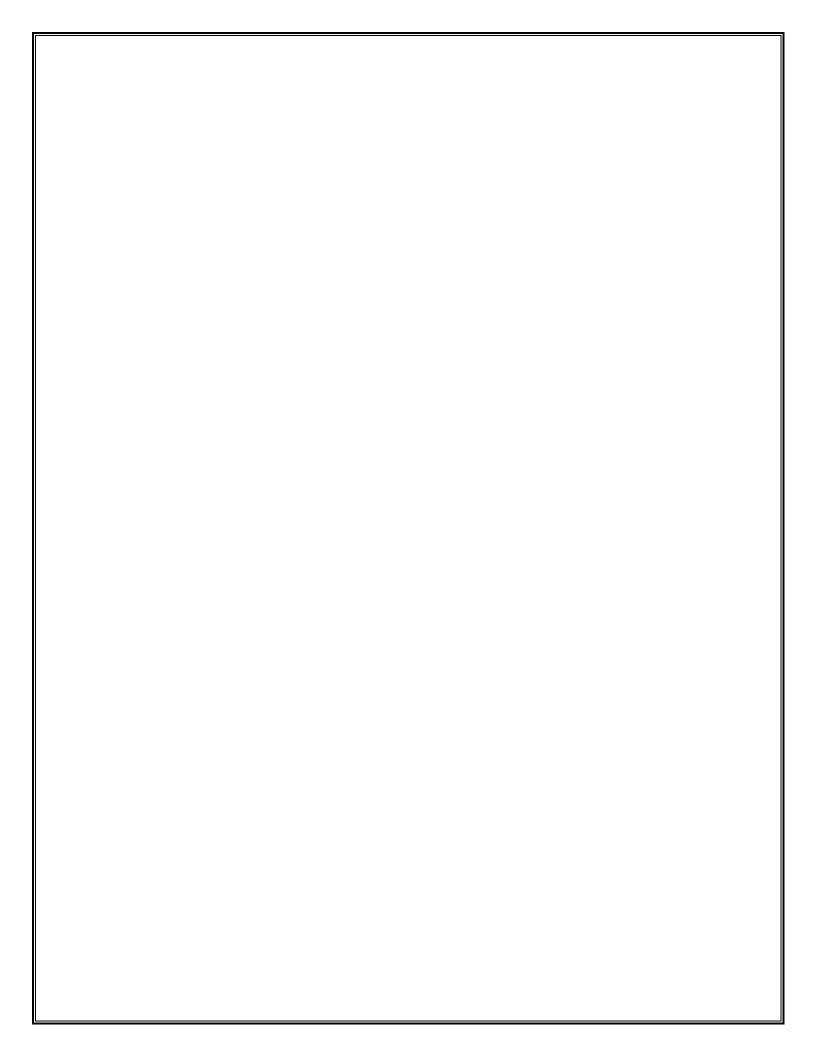

fig: phenomenon at pN-junction.

As shown to fig, PN junction is formed when thin layers of p and N -type semiconductors are joined together that results in the

following phenomenon.

- \* The majdity holes from p-fide deffuse into N-fid and vice verpa.

- \* Recombination of electrons and holes in a narrow Region on both sides of the junction repulte in uncovered fixed positive ions on N-side and fixed negative ions on P-sides.

- \* This is the Depletion region where no free elected and holes present

- \*The electric field per up by the positive and negative ions prevents further flow of electrons and holes.

- + The electric field causes the movement of minority Carriers in opposite direction that provides a minority carrier drift whent.

- \* In steady state there is no net wearnt flow across the junction.

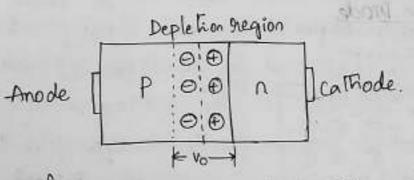

The simplified diagram of an open inclust pN junction deade as shown in fig below, where vo is the constant potential. The p-side terminal is called anode and the N-side terminal is the cathode

fig: An open circuited PN Junction.

### PN-Junction Diode:

PN jurchen Diode hap a ability to permit a current flow when it floward biaped and it blocks the current flow when it is severe brazed hence it can be used as the "Switch".

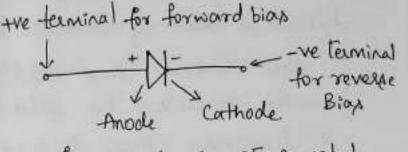

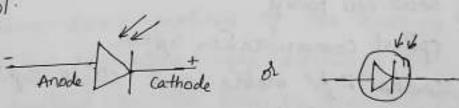

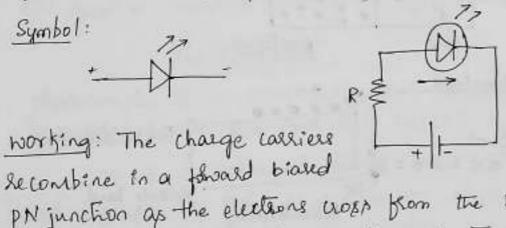

The Switch is said to be 'ON' when it is flow brased and 'OFF' when it is reverse brased. It is provided with the copper wire connecting leads becomes an electionic device known as a Drode. The circuit symbol of pN-junction drode and cht symbol in the fig below.

fig: AN Junction Diode.

fig: Diode ciemit symbol.

The circuit symbol of a deode is an arrowhead and a bar. The arrowhead Indicates the flow desections of the arrivent when it is forward biased.

A PN junction diode can be destroyed by a high level of forward current overheating the device. It can also distarged by a large reverse voltage causing the junction to breakdown. In general, physically large diodes paps the largest currents and survive the largest reverse voltages. We can classify PN junction diodes as low current, medium current and High current Diodes.

The low current device may be of size 0.3cm long, the cathode is usually denoted by a colorised band, and is capable of passing a maximum current of 100mA (75V).

The medizion warent diode can pass a followood warent of about 400mA and survive over 2000. of reverse voltage. The anode and cathode terminals are indicated by a diode symbol on the side of the Diode.

High misent deodes of power deodes can pass forward misente of many amperes and can purvive several hundred volle of reverse beap.

tow unent and medirem uneent diodes are usually morinted by soldering the connecting leads to terminals. Power dissipated in the device is carried away by airs conkections and by heat conduction along the connecting leads. Air convection is inadequate in power diodes hence these diodes are designed for mechanically connecting to metal heat sink.

Biaking: Applying External voltage to any electronic component à called Biaking. PN Junction Can be Operated in three modes. is unbiaked pN Junction of forward Biaked pN Junction it Reverse Biaked PN Junction.

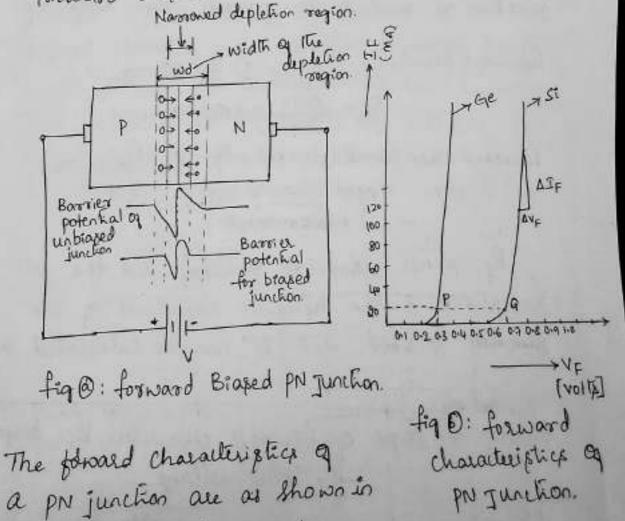

Forward Biasing of PN Junction Forward Characteristics of PN Junction.

A positive bias vlg is applied to the p-side and the negative bias vlg is applied to the N-side of the PN Junchon is called Forward Biasing.

In p-side holes are the majority carriers and in the N-side electrons are the majority carriers. As the holes on the p-side are trely charged particles they are repelled from the positive bias voltage.

Forward characteristics is plot of forward voltage. (VF) versus forward current (IF). From these weves we see that the little forward werent flows until VF Exceeds the junction barrier potential 0.3 for Ge and 0.7 for Si

Withe the increase in VF towards the knee characteristics. the poorrier potential gradually reduced Beyond the knee voltage the poorrier voltage is fully overcome and IF increases with increases in VF and thus thes behaviour of plocking is termed as resistance. The forward biased PN junction is said to be provide low resistance.

Forward Resistance (at point 9) for sikcon.

$$R_{f} = \frac{0.7V}{2000A} = 350hmg.$$

Forward Presiptance (at point p) for Germanium.  $R_f = \frac{0.3V}{dom A} = 15$  ohms.

Re is not used in practise. Id, the ac repistance & the dynamic repistance of the junction is used. and it can be calculated as

$$\mathcal{X}d = \frac{1}{\operatorname{slope} q} \quad \begin{array}{l} \text{forward characteristic beyond} \\ -\text{the gree voltage} \end{array}$$

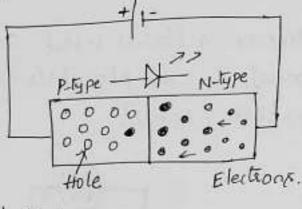

and are forced to move towards the junction. 111 y the electrons on N-Ride are repelled by the Application of the -ve bias voltage and are move towards the junction. Due to this the depletion region is narrower down, and also the barrier potential is reduced as shown in feg @.

As the applied voltage is increased from 'o' the parrier potential gets gadually too small and becomes disappeared and the charge carriers readily more from p to N and N to p freely Thus the werent flows and the junction is forward brased

fig D, for the pelicon and Germanium

semiconductors

Forward characteristics is plot of forward voltage (VF) versus forward current (SF). From these waves we see that the little forward werent flows until VF Breeds the junction barrier potential 0.3 for Ge and 0.7 for Si

With the the increase in VF towards the knee characteristics. the porrier potential gradually reduced Beyond the knee voltage the porrier voltage is fully overcome and IF increases with increases in VF and thus these behaviore of plocking is termed as registance. The forward biased PN junction is said to be provide low resistance.

Forward Repistance (at point 9) for sekcon.

$R_f = \frac{0.7V}{2000A} = 350hms.$

Forward Presistance (at point p) for Germanium.  $R_f = \frac{0.3V}{dom A} = 15$  ohms.

Re is not used in practise. I.d. the ac represtance & the dynamic resistance of the junction is used. and it can be calculated as

$$\frac{d}{d} = \frac{1}{\frac{\Delta IF}{\Delta V_{F}}} = \frac{1}{\frac{\Delta V_{F}}{\Delta V_{F}}} = \frac{1}{\frac{\Delta V_{F}}{\Delta V_{F}}}$$

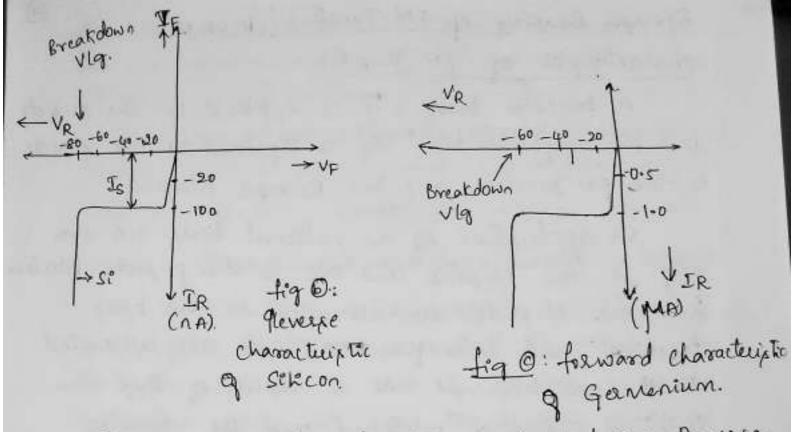

# Reverse Brazing of pN Junction Reverse

Characteristic of pN Junction.

A positive bias vig is applied to the N-Nide and the negative bias vig is applied to the p-side of the pN junction is called Reverse Brasing.

On application of an external bios inertive vlq to the N-side and we to the p-side. Election from the N-side are attracted to the bias terminal and holes from the p-side are attracted to the we terminal. As a result of this, the depletion region is widered and the bassier potential is threesed by the magnetude of the applied voltage. Dute to the increase in basever potential and the Resultant electric field. It is not possible for the majority current to flow awass the junction and the junction is said to be reverse brazed as shown in fig @.

Widered Bepletion region. Widered Bepletion region. Peoles N eoles N eo

Scanned by CamScanner

Reverse Bras characteristic is the plot of Reverse Voltage (VR) versus Reverse current (JR). Reverse Bras Characteristics for si and ge is ashown in tig D & O Lespectively.

A Small reverse brax voltage & enough to pull across the available minority caesies across the junction. When all the minority charge carriers have copped over, further increase in bias voltage will not increase the warnt. This is called Reverse saturation current (Is).

The Reverse saturation current (Is) is very much smaller than the followed current (IF). i.e Is is negligible composed to IF. Hence a reverse biased diode inay be considered as open pointch.

At porr koular value of Reverse vig. the severe outernt suddenly shoot up, resulting in overheating and the deode is said to be in the "Breakdown region"

Scanned by CamScanner

The breakdown voltage for sition pN junction is about Sov and for germanizem pN junction is about 60V as Shown in fig @ and @.

From the reverse characteristics. we can find the Reverse resistance as below.

for St. VR= SOV, IS=LOONA

Reverse Resistance, Ro = VR = 50V = 50M.D.

The Diode Current Equation:

The General characteristics of the PN Junction are defined by the following Diode current Equation.  $\boxed{I = I_0 \left[ e^{\frac{1}{7}N} - I \right]}$

where,

$$I = Diade cuarent$$

$T_0 = Reverse Saturation unevent$

$V = Applied voltage$

$\eta = Constant$ ;  $\eta = 2$  for  $Si$ ,  $\eta = 1$  for  $Ge$ .

$V_T = volt equivalent g temperature = \frac{T}{11600}$

At room temperature  $T = 300^{\circ} K$  :  $V_T = \frac{300^{\circ} K}{11600}$

From the forward characteristics it is observed that forward whent is zero up to a certain forward vlg`vir. This vlg is called as "<u>cut-in voltage</u>. It is the vlg at which the diode start conducting. As the voltage is indeased beyond the cut-in vlg Vs. the current indeases scapidly. The cut-in vlg is sometimes called "effort vlg" & "breat point vlg" of "threshold vlg".

cut in vig differs for different semiconductor material and different method of fabrication. At 200m temperature, the cut in vig for Ge is 0.2 and for selecon it is about 0.64.

The Diode autent Equation for Reverse Bras. eve ver is Ð Reverse braze of PN junction

Scanned by CamScanner

Variable reverse blas voltage is applied accoss the pN jusction didde as shown in fig. The Didde current equation is

$$I = I_0 \left[ \frac{v}{nv_T} - 1 \right]$$

when the severe of negative vig is applied alongs the diode. V is negative and  $I = I_R$  and when  $V \gg V_T$  is negative and  $I = I_R$  and

$$e^{-v/\eta V_T} = \frac{1}{e^{V/\eta V_T}} \ll 2$$

Hence, the above current diode equation reduces to  $I_R = -I_0$

The above equation shows that the unkent is constant and is independent of the applied severe bras. when the Reverse vig is increased to VRB, breat down occurs.

Note: The Diode current equation is not applicable during Break down.

Examples:

1) For a sikcon diode at a working temperature of 25°C the forward voltage applied across the diode is 0.5V. Determine its forward current if the reverse saturation current is 10nA.

Soln: Forward werent. IF = Io [ envi 1]

Given:

$$I_0 = Reverse saturation current = 10nA = 10x10^9A.$$

$V = forward voltage across the diode = 0.5V$

$T = 25^{\circ}c = 25+273 = 298^{\circ}5.$

$\therefore V_{\pm} = \frac{T^2}{2} = \frac{298}{25.68mV.}$

Scanned by CamScanner

(6)

$$\gamma = 2$$

for Ritcon.

$I_F = 10 \times 10^9 \left[ e^{\frac{0.5}{8 \times 2.5 \times 10^3}} - 1 \right]$

$I_F = 0.169 \text{ mA}$

2) A Germanium diode draws 40mA with a flward bias of 0.25v. The junction is at room tempulative of 293K calculate the Reverse saturation current. Take n=1

<u>Soln</u>: Given:  $I_F = 40mA$  V = 0.25V T = 2.93 K  $\eta = 1$  $V_T = \frac{293}{1600} = 0.025$

$$\begin{split} \overline{I}_{F} &= \overline{I}_{\delta} \left[ \frac{\overline{e^{\gamma_{W_{T}}}}}{\overline{e^{\gamma_{W_{T}}}}} \right] \\ \overline{I}_{\delta} &= \frac{\overline{I}_{F}}{\sqrt{\gamma_{W_{T}}}} \\ &= \frac{\sqrt{\gamma_{W_{T}}}}{\frac{\sqrt{\gamma_{W_{T}}}}{\frac{\sqrt{\gamma_{W_{T}}}}{\frac{\sqrt{\gamma_{W_{T}}}}{\frac{\sqrt{\gamma_{W_{T}}}}{\frac{\sqrt{\gamma_{W_{T}}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\sqrt{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{W}}}{\frac{\gamma_{$$

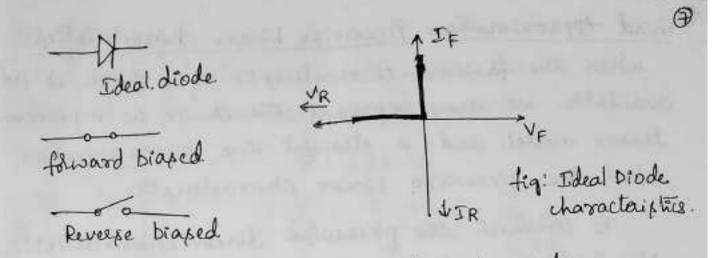

Ideal Diode Characteristics: [Ideal Diode Approximation]. An ideal diode is one which has following characterister by The cut-in voltage is zero, since there is no barrier potential. any small forward braz voltage causes conduction through the devices. If The followed resistance is zero. If The Reverse resistance is reco. The Reverse resistance is reco. The Diale readily conducts when it is forward brazed and it blocts conduction when it is presed brazed The reverse saturation current is zero.

An ideal diade acts as a prosten. An ordinary proster has zero registance when it is closed and infinite resistance when it is open. The switch is said to be close when it is foperand brazed and prosted is said to be open when it a reverse prased.

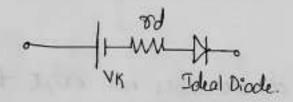

# Diode Approximations.

In practice an ideal diode does not exist, there are many applications where diodes can be assumed to be near ideal devices.

### Second Approximation:

Diodes are assumed to be nearly ideal for setuations which require exact values & load current and load vlg but ideal diodes does not exist in practical cituations. Hence we assume the second approximation model In this we consider vg deop of schicon 0.7v and gamanium as 0.3v. Constant vig source og 0.7v de 0.3v is assumed to be in series with Ideal diode. as shown in fig.

A H H X Jdeal diade. The VE VE VE ₩1,0.3V WIR. fig: Second approximation. fig: Approximate characteristices for

Scanned by CamScanner

# Third Approximation: Piecewise Linear characteristics.

when the faward characteristic & a diode is not available we may represent the device as a piecewise lenears model and A-straight-line approximation Called the precewire Linear characteriptic.

To construct the piecewise linear characteriptic. VE is fight marked on the horizontal axis, as shown in fig. - then starting at VF. a straight line is drawn with a plope equal to the diade dynamic resistance.  $(MA) \left( (V + \Delta V_F) \right)^B$

fig: Third Approximation Cht.

0.204 0.6A tig: precewise Linear characteristics of a diode.

Drade Appres

12.0 80

40

ex: construct the piecewise - kinear characteristic for a pekcon deode that has a 0.45, Dynamic resistance and a 200mA naximum forward current Given: VF= 0.7V., od= 0.4.2, IF (max)= 200 mA. Vr = V IExag 1 - 100 B. = 200mA x 0.4 AV = 0.08V Point A at VF=0.7. and point B at IF = 200MA. Draw a pleaight line

Examples:

6

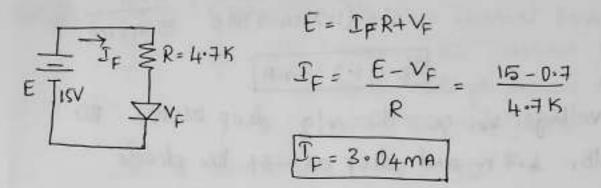

i) A selecon d'ode is used in the circuit as Shown in fig. Calculate Diode merent.

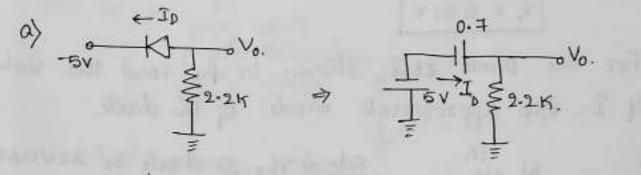

» For the Diade ciecuit, Determine Ip & Vo using approximation model.

Applying KVL,  $5 = 0.7 + 2.2 \times 10^3 I_D$ .  $I_D = \frac{5 - 0.7}{2.2 \times 10^3} = 1.954 \text{ mA}.$

Vo is the voltage access the 2.25 repiptor.

$$V_{0} = 2 \cdot 2 \times 10^{3} \times 1 \cdot 95 \times 10^{3}$$

$$V_{0} = 4 \cdot 29V. = 4 \cdot 3V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

$$V_{0} = 5V - 0 \cdot 7 = 4 \cdot 7V$$

Applying KVL,  $8V = 1 \cdot 2 \cdot 5 \times I_D + 4 \cdot 7 \times I_D + 0 \cdot 7$ .  $8V = I_D (1 \cdot 2 \cdot 5 + 4 \cdot 7 \cdot 5) + 0 \cdot 7$  $I_D = \frac{8 - 0 \cdot 7}{(1 \cdot 2 + 4 \cdot 7) \times 10^3} = \frac{7 \cdot 3}{5 \cdot 9 \times 10^3}$

ID = 1-237MA

Olp voltage vo pr the vlg drop accord the repristor 4.7K and drop arrough the diode.

$$V_{0} = I_{0} \times 4.7 K + 0.7$$

= 1-237×10<sup>3</sup>×4.7×10<sup>3</sup>+0.7

$V_{0} = 6.51 V$

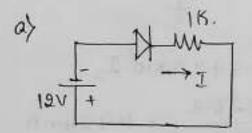

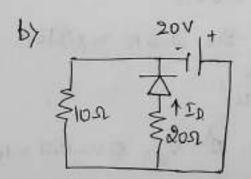

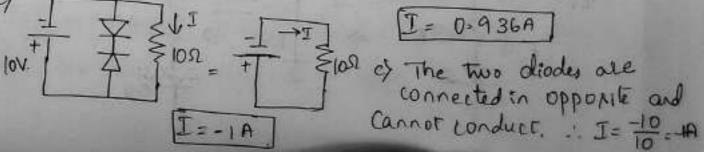

3) For the Diode chts shown in fig. Find the value of I. Use approximate model of the diode.

<u>solnio</u>) The si deode is reverse brazed by 12V, so it does not conduct.

D'The voltage accoss the diode branch is low which is independent of resiston 10.92.

Therefore,

$$I = \frac{20 - 0.4}{20} = \frac{19.3}{20}$$

Scanned by CamScanner

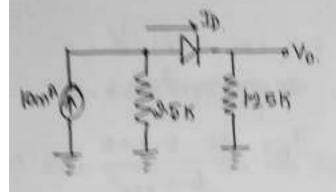

For the deade the shown determine VOR ID.

- Vo. Soln: The given we wit SAGE SMORE COntains mucht pource. convert the undert source into voltage ponse in peries with the registance.

V = 10×103× 2 5×10

V= OEV.

C)

Replacing wavent source by vig ponsie the circuit " will be > any with

Applying KVL. 25 = 2.5×10 × ID+0.7+1.25×10×ID TD = 05-0.7 (0.5+1.25) ×103 ID= 6.48MA

output vlg will be the deop accors the sexistor 1-25K. .. Vo= 1-25KxJD

No- 8.1V

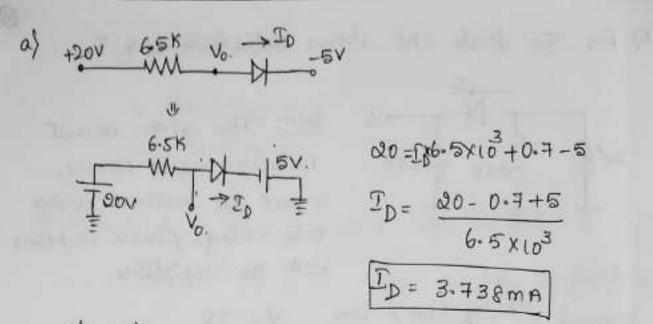

Determine the Drode wegens and the output vig. for the circuits shown in fig.

olp voltage vo is the Defference blue the applied voltage applied and the vig deop accoss the 6.5%.

b) Si 4.5K  $12\sqrt{V_{01}}$  Vor Determine Vor & Vor for the  $\frac{1}{2\sqrt{V_{01}}}$   $\frac{1}{\sqrt{Q_2}}$   $\frac{1}{\sqrt{Q_2}}}$   $\frac{1}{\sqrt{Q_2}}$   $\frac{1}{\sqrt{Q_2}}$   $\frac{1}{\sqrt{Q_2}}}$   $\frac{1}{\sqrt{Q_2}}$   $\frac{1}{\sqrt{Q_2}}$

$\therefore$  I= <u>12-0.3</u> = **1**.7 MA. Vo=1Kx11.7m=11.7 ·· Vo= 11.7V

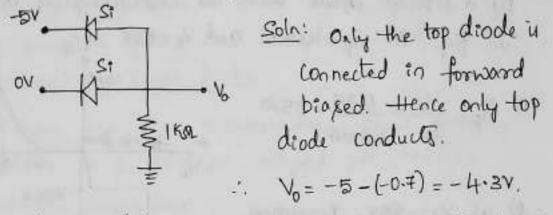

=> Determine Vo for the negative logic OR gate.

The output will be Vo= -4.3V (high of negative logic) for input - 5V and the autput will be zero (low) if the inputs are zero.

8) Determine Vo for negative logic AND gate as shown In \$9. Soln: The lower diode will conduct

-5V Vo=OV. If both the inputs are ov, both -ovo diodes conduct Vo=OV(LOW, 0). If -1both inpute one -5v, both diodes J-5v do not conduct, Vo=-5v (high 1) - 5V = high and ov = low, o.

This is negative AND.

0V\_\_\_\_

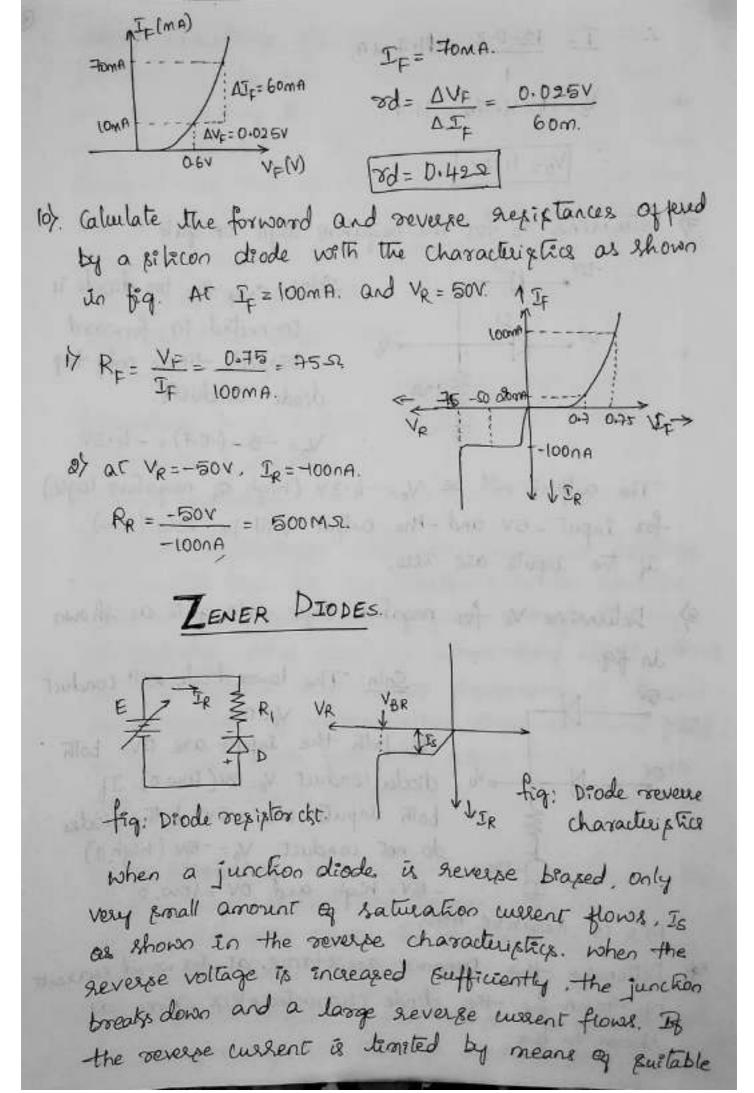

of Determine the Dynamic Resistance at for word waren's of tomA for the diode characteristics given as Shown in fig.

Scanned by CamScanner

Series registance, the power digging ation in the junction can be kept constant to a level that will not destroy the device. In this case the diode may be operated in the reverse breakdown. Diodes designed for this operation is reverse breakdown are found to have a breakdown vig that remains extremely stable over a wide range of werent levels. This property gives the breakdown diodes of are also called as <u>Kener Diodes</u>.

These are two mechanisms that cause breatdown in a reverse brazed prijunction. It Avalanche breat down. It Avalanche breat down.

Avalanche Breakdown: when the breakdown voltage is greater than 60, the electrons in the reverse saturation current can be given enough energy to diplodge other electrons when they strike atoms in the depletion region. This phenomenon is known as ionization by collision. When these electrons freed in this way collide with other atoms they release more flee electrons, producing a chain or avalanche effect.

<u>Kener Breakdown</u>: When a diode is heavily doped, the depletion layer becomes very narrow. Because of this, the electric field across the depletion layer becomes very narrow. Because of this. The electric field across the depletion region is very interve. The field strength is strong enough to disladge electrics from their

Valence orbits. The Reakon of the elections in this manner is known as <u>kener effect</u>.

Even though zener and avalanche are two different breakdown mechanizmy. The term zener deode is used appleed to all breakdown diodes.

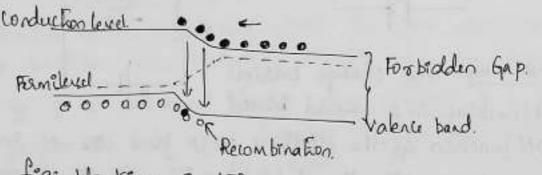

#### Carcuit Symbol:

The circuit symbol for zener drode is some as that of the ordinary diode but cathode bar it approximately in the shape of letter Z

The arrowhead on the symbol indicates the filow of direction of forward current. Voltage deep Vz is positive on the cathode and negative on the anode.

Anode N Calhode Negative popitive terminal -terminal for for zener Operation. Xener Operation fig: unir Symbol.

Zence Diode as a Voltage Regulator

Voltage Regulators are the devices used to maintain Constant Voltage accoss load despite of fluctuations in the input voltage and load currents.

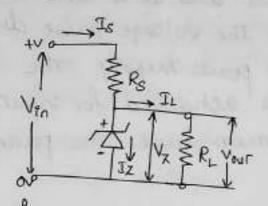

The zener diode in its reverse bias &lgion is widely used as a voltage regulator as ir continues to operate till the magnitude of current becomes less than Iz(min) The typical zener voltage regulator as shown in fig:

fig: Zener diode as a Voltage Regulator The zener deode of breakdown Voltage Vz is connected to the input supply in reverse direction. For all the values of when within the breakdown region, the vig access the deode will remain fixed at Vz. giving Constant

Supply accoss the load. The Refistance Rs controls the current flowing in the circuit.

Caseiz: when there is no load connected [IL=0].

The warent flowing in the circuit entactly posses through zeres deade. The Deade dissipates maximum power thus utmost care must be taken while selecting the series resistor so as to maintain the power dissipation within the large of maximum power dissipating capability of the deade. <u>Capeling When the load resistance R is connected</u> across the diade

Since the deode is porralled to the 40nd the vig anors the load is equal to the Vz. The Zener werent must always be above Filmer). The Voltage regulation Can be done through two techniques & Line Regulation. It hoad Regulation.

that load statistic ve long

1. Line Regulation:

In this case serves resistance and load resistance are kept constant and it is assumed that all the variation in the voltage arise due to fluctuations in input power supply. The regulated output voltage is achieved for input voltage above certain minimum level. The percentage of regulation is given by.

where, vo is the output vlg.

Ven is the input vig.

Avo is the charge in the output voltage for a particular charge in input voltage Avin.

2. Load Regulation:

In this, the input voltage is fixed while the load resistance is varied. The output voltage is obtained as long as the load resistance is maintained above a minimum Value. The percentage of regulation is given by.

VNOLOAD - VFUII Load VFull load

and the star  $= \frac{V_{NL} - V_{FL}}{V_{FL}} \chi \log \theta$

where,

10 och

VNL = Voltage accoss the diode when no load is applied VFL = Full load resistor voltage

Difference between Avalanche Break down &

Zener Breakdown.

| Avalanche Breakdown                                                                                    | Zener Breakdown.                                                                                                       |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 17 Take place in lightly<br>doped deodes                                                               | to Take place in heavily<br>doped diodes.                                                                              |

| et occurs at higher<br>reverse voltage                                                                 | & occurs at lower<br>reverse voltages.                                                                                 |

| Carrier multiplication<br>is present                                                                   | 37 carrier multiplication<br>is not present.                                                                           |

| H) It desteays the<br>junction                                                                         | H} It will not destady<br>the junction                                                                                 |

| 5> Depletion region is<br>wider                                                                        | 5) Depletion region is<br>small                                                                                        |

| 67 It is gradual                                                                                       | 67 It is phase and<br>pudden.                                                                                          |

| FORMU                                                                                                  | LAE                                                                                                                    |

| 17 O/p vlg $V_0 = Zener Vlg V_Z$<br>i-e $V_0 = V_Z$<br>a) current in the current is<br>$I = I_L + I_Z$ | =+> i> Rmin = $\frac{V_{i}C_{max}-V_{o}}{I_{a}(max)+I_{u}}$<br>i> Rmax = $\frac{V_{i}(min)-V_{o}}{I_{a}(min)-V_{o}}$   |

| 3) zener warent, Iz = I.                                                                               | $-I_{L} = \frac{V_{o}}{I_{L}}$                                                                                         |

| $H_{7} = IR + V_{0}$ $S = \frac{V_{0} - V_{0}}{R}$                                                     | $\frac{1}{I_L}$ $\frac{1}{P_Z(max)} = \frac{1}{I_Z(max)} \frac{V_Z}{V_Z}$ $\frac{10}{I_Z(max)} = \frac{P_Z(max)}{V_Z}$ |

| $\frac{6}{R} = \frac{V_{i} - V_{o}}{I_{z} + I_{L}}$                                                    | Vz.                                                                                                                    |

Scanned by CamScanner

3

1) For

$$Vi(min) \in I_{Z} = I_{Z}(min)$$

$I = T_{Z}(min) + I_{L}$

$\therefore Vi(min) = JR + V_{0}$

12) For  $Vi(max) : I_{Z} = I_{Z}(max)$

$I = I_{Z}(max) + I_{L}$

$Vi(max) = IR + V_{0}$

Paoblems:

1) For the circuit as shown in fig. tenes dicode

$a connected accops the loadd

a) For  $R_{L} = 1805$ . delimine all currents 8 voltages

b) Repeat part (a) for  $R_{L} = 4505$

chind the minimum value  $GR_{L}$  for the zener

$J_{0}$  be in on ptate.

$M$ ,  $I = S_{Z} + I_{L}$  ,  $V_{0} = V_{Z}$

$T_{Z} = 0 \Rightarrow T_{L} = I$

then,  $T_{L} = \frac{20}{200 + 180}$

$T_{L} = \frac{52 \cdot 6mR}{200 + 82}$

$V_{Z} = V_{L} = 20 - (Roo x 52 \cdot 6x \cdot 10^{2}) = 9 + 48 < 10x$

$R_{L} = 450$ .

$I = \frac{20-10}{200} = 500R$

$V_{L} = V_{Z} = 10$ .

$I = \frac{V_{0}}{R_{L}} = \frac{10}{450} = 22 \cdot 2mR$

$T_{Z} = 50 - 22 \cdot 2$

$R_{Z} = 27 + 8xio = 248 min$$

(a) When the zeries draws maximum power.

$$I_{\lambda} = \frac{360}{10} = 35 \text{ m A}.$$

$$I_{\lambda} = \frac{360}{10} = 35 \text{ m A}.$$

$$I_{\lambda} = \frac{360}{10} = 35 \text{ m A}.$$

$$I_{\lambda} = I = I_{-1}I_{z} = 50 - 2.5 = 15 \text{ m A}.$$

$$R_{L} = \frac{10}{15 \times 10^{3}} = 663 \Omega.$$

(b)  $I_{\chi} = 0 \text{ (just to on state)}$

$$I = 50 \text{ m A} = I_{L}$$

$$V_{L} = V_{Z} = 10V$$

$$R_{L} = \frac{10}{50 \times 10^{3}} = 200\Omega.$$

(c) Determine the sange of V. which zeries diode conduct.

Given:  $R = 220\Omega$

$$R_{L} = 1 - 25 \text{ K}$$

$$V_{Z} = 20V$$

$$R_{\chi} = 1 - 20 \text{ m M}.$$

$$I = I_{L} = \frac{20}{1025 \times 10^{5}} = 16 \text{ m A}.$$

$$V_{L} = 20 \text{ V}. \quad I_{\chi} = 0.$$

(f)  $V_{\chi} = 20 \text{ V}. \quad I_{\chi} = 0.$

$$I = I_{L} = \frac{20}{1025 \times 10^{5}} = 16 \text{ m A}.$$

$$V_{L} = 1200 \text{ m M}.$$

$$I_{L} = 16 \text{ m A}.$$

$$I_{L} = 20 + 16 \text{ m A} = 316 \text{ m A}.$$

$$I_{L} = 16 \text{ m A}.$$

$$I_{L} = 10000 \text{ m A}.$$

$$I_{L} = 1000$$

For input voltage from 23.52 V to 36.72 V. VL Will remain constant at 20 V.

3) For the network shown in fig. determine The range of RL<IL that will regult in VR, being mentained at LOV. Also determine wattage rating of diode.

$$\begin{array}{cccc} \underline{Given}: & R=115 & & & & & & & \\ Vin = 50V. & & & & & \\ Izlmin] = 32mA & & & & & \\ V_2 = 10V. & & & & & \\ V_2 = 10V. & & & & \\ Izlmin] = 32mA & & & \\ \end{array}$$

Value & RL. that will turn zerer deode on.

$$R_{Lmin} = \frac{R.V_2}{V_1 - V_2} \left[ voltage divide_] \right]$$

120 9 2 44

Voltage accoss R, i.e.  $V_R = V_1 - V_2 = 50 - 10 = 40 V.$

$$\frac{L}{R} = \frac{40}{1000} = 40 \text{ mA}.$$

ILLMAN = I - IZ(MAR) = 8MA.

$$R_{L} \max = \frac{V_2}{I_z(\min)} = \frac{10}{8m} = 1.2K\Omega$$

$$Pmax = V_T I_Z = 320mb$$

A

4) Design a Xere regulator to meet the following

speer is cations.

b old vile to est load whent tome.

cation is zeree power,

$$P_2(max) = 500 \text{ mw}$$

.  $J_2(min) = 5 \text{ me}$ .

cation is the value of  $P_2(max) = 500 \text{ mw}$ .

$J_2 = 100 \text{ me} \text{ Treas} = 500 \text{ mw}$ .

$J_1 = 100 \text{ me} \text{ Treas} = 500 \text{ mw}$ .

$J_1 = 100 \text{ me} \text{ Treas} = 500 \text{ mw}$ .

$J_1 = 100 \text{ me} \text{ Treas} = 500 \text{ mw}$ .

$J_1 = 100 \text{ me} \text{ Treas} = 500 \text{ mw}$ .

$J_1 = 100 \text{ me} \text{ Treas} = 500 \text{ mw}$ .

$J_1 = 100 \text{ me} \text{ Treas} = 130 \text{ me} \text{ mw}$ .

$V_1(max) = 15 - 2 = 130 \text{ me} \text{ mw}$ .

$V_1(max) = 15 - 2 = 130 \text{ me} \text{ mw}$ .

$V_1(max) = 15 + 2 = 170 \text{ me} \text{ me} \text{ mw}$ .

$V_1(max) = 15 + 2 = 170 \text{ me} \text{ me} \text{ mw}$ .

$V_1(max) = 15 + 2 = 170 \text{ me} \text{ me} \text{ mw}$ .

$V_1(max) = 15 + 2 = 170 \text{ me} \text{ m} \text$

$I = J_{k} + I_{z}$  = 90 + 20 = 30 mA.  $J = \frac{V_{i}^{*} - V_{0}}{R} \implies R = \frac{V_{i} - V_{0}}{I} = \frac{16 - 10}{30 \times 15^{3}}$   $R = 200\Omega$

6) A 10V zenes is connected for voltage regulator as shown in fig. If the load current is 6mA. find I & Iz.

R = 1K  $V_{0} = J_{L}R_{L}$   $V_{0} = 6 \times 10^{3} \times 1 \times 10^{3} = 6V.$   $V_{1} = V_{0} = 6V.$   $V_{2} = 6V.$   $I_{2} = 0 \quad X \quad I = 6 \text{ mA.}$   $I = I_{L} + I_{2} = 6 \text{ mA.}$

Since diode is in parallel with RL. the device is low zenes. it cannot conduct and is open.

= Deve what range of input vig will the zerve circuit phown in fique maintain 300 across 2002 load assuming that series resistance R= 2005 and -the zerve current raking is 25mA.

it The minimum slp vlg is required will be when Iz=0 and I=IL

$$\frac{\Gamma_{L}}{R_{L}} = \frac{30}{2K} = 15 \text{mA.}$$

$$\left[\Gamma_{L} = 15 \text{mA.}\right]$$

: Minimum Jp Vlg = V0+JR = 30+ (15×10×200)

when  $S_{Z} = Max$ . i.e.  $I_{Z} = 25mA$ .  $I = I_{L} + J_{Z} = 15 + 25m = 40mA$ .

$$\begin{array}{l} \text{Maximum Illy Vlg} = V_0 + JR \\ = 30 + (40 \times 10^3) \times 200 \\ \hline V_{11} \text{Max} = 38 \text{V} \end{array}$$

: input voltage range is 33V to 38V to get sov. 6) A zener diode shown in tig has  $V_{z}=18V$  The vig areas the load stays at 18V as long as  $I_{z}$  is maintained blw 200mA and 2A. Find the value of Staies resistance so that Vo remains 18V while the input voltage V; is free to vary from sov to sov.  $V_{z}=18V$  R=?  $V_{z}=18V$  R=

G

$I_X(min) = 200 \text{ mA}$  when  $V_1(min) = 22V$ . · IL remain unchanged -1  $I_L = \frac{V_0}{R_L} = \frac{18V}{18\Omega} = 1A = 1000 \text{ MA}.$ R= Vin-Vo = 22-18 Iz+IL (200+1000)×103 - piter of E round to the R= 3.332 9) Design a Zener Regulator for the given specification 17 SIP DC IS IOV ± 2V a) ofp requirements are 54, 20mA. 3) Assume Izimin) = 5 mA. Izimax) = 80mA. Given: VZ=Vo=5V V = 12 V AVE TRADATION I= 20mA Iz= 5mA when V2n= 10-2V=8V Iz=80MA when Vin=10+2=12V. \* IL= 20MA and voltage across the load No=5V. The load weekner stays constant i.e  $T_L = \frac{V_0}{R_L} \Rightarrow R_L = \frac{5}{20MA} = 250\Omega$ Saies Resiptance  $R = \frac{V_{in} - V_0}{2} = \frac{8 - 5}{2}$  $\frac{1}{J_{z}(min) + J_{z}} = \frac{3 - 5}{(5 + 20) \times 10^{3}} = \frac{3}{25 \times 10^{3}}$ R= 1202 S - 9 10% Design a zener Regulator for the given ppecification is old Nd = EN as IT = 10MA 3> bx(max) = 400mw Hy slp vlg = lov t 2v

Solit: Given:

$$V_0 = V_Z = 5V$$

$\Gamma_L = 10mR$

$V_1(min) = 10-2 = 8V$

$V_1(max) = 10+2 = 15V.$

$R_L = \frac{V_0}{J_L} = \frac{5}{10 \times 10^3} = 0.55K$

$R_L = 500.9$

Max zener current.  $J_Z(max) = \frac{100mW}{5V} = 80mR$

Minimum Slp vlg sequired when  $T_Z = 0$

$T = T_L = 10mR.$

$V_1(min) = 10-2 = 8V$

$V_1(mix) = 10+2 = 12V$

$V_1(mix) = 10+2 = 12V$

$Rmax = \frac{V_L(min)-V_0}{10+0} = \frac{8-5}{10mR} = 300S.$

$T = T = T < R < 300S$  is quit voised for providing

a SAV stabilized supply is a variable load.  $T_B$

the input voltage is  $32V$ . (alulate

is The value q serier Seriptione sequired

$IV$  Diade unsent when the load is 1200S and

$R = 400S.$

$V = \frac{V_L - V_Z}{T_Z + T_L}$

$$I_{L} & R_{L} \quad \text{is not given . So } I_{L}=0$$

$$\therefore R = \frac{V_{tn} - V_{2}}{I_{Z}(\max)}$$

$$R = \frac{V_{tn} - V_{2}}{I_{Z}(\max)}$$

$$R = \frac{V_{tn} - V_{2}}{V_{X}}$$

$$R = \frac{V_{tn} - V_{2}}{V_{X}}$$

$$R = \frac{V_{tn} - V_{2}}{V_{X}} = \frac{W_{1}}{W}$$

$$R = \frac{32V - 24V}{26mA} = 22\Omega$$

$$R = \frac{32V - 24V}{26mA} = 22\Omega$$

$$R = \frac{32V - 24V}{26mA} = 20MA.$$

$$I = \frac{V_{tn} - V_{0}}{R_{L}} = \frac{32V - 20}{400\Omega} = 20MA.$$

$$I = \frac{V_{tn} - V_{0}}{R} = \frac{32V - 20}{400\Omega} = 20MA.$$

$$I = I_{Z} + I_{L}$$

$$I_{Z} = I - I_{L} = 20 - 20 = 0 \Rightarrow I_{X} = 0$$

when  $R_{L} = 1200\Omega$ . Werent  $I_{X} = 0A.$

$$R = 1200\Omega$$

$$V = 5V \quad SV \quad I_{L} = 20MA \quad SV = 500MO$$

$$V = 5V \quad V_{Z} = 5V, \quad I_{L} = 20MA.$$

$$R_{L} = \frac{V_{0}}{V_{0}} = \frac{5V}{20MA} = 250M$$

(\*)

d:

$$J_{x}(max) = \frac{P_{x}(max)}{V_{x}} = \frac{600 \text{ mW}}{5 \text{ v}} = 100 \text{ me}.$$

d:  $J_{x}(max) = \frac{15 \text{ V} - 5 \text{ V}}{5 \text{ L}(max) + J_{L}(max)} = \frac{15 \text{ V} - 5 \text{ V}}{100 \text{ m} + 20 \text{ m}}$

$\frac{14}{20 \text{ m}} = \frac{15 \text{ V} - 5 \text{ V}}{5 \text{ L}(max) + J_{L}(max)} = \frac{15 \text{ V} - 5 \text{ V}}{100 \text{ m} + 20 \text{ m}}$

$\frac{14}{20 \text{ m}} = \frac{15 \text{ V} - 5 \text{ V}}{5 \text{ L}(max) + 32 \text{ L}(max)} = \frac{15 \text{ V} - 5 \text{ V}}{100 \text{ m} + 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{10 \text{ V} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{10 \text{ V} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{10 \text{ V} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{100 \text{ J} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{100 \text{ J} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{100 \text{ J} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{100 \text{ J} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{100 \text{ J} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{100 \text{ J} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{100 \text{ J} \pm 20 \text{ m}}{100 \text{ m} \pm 20 \text{ m}}$

$\frac{16}{20 \text{ m}} = \frac{50 \text{ m}}{100 \text{ m}} = \frac{100 \text{ m}}{100$

Rz=0. Find the large of RL and IL for load Voltage to be constant. what is the maximum vig of the diode. Rs Is 1K MW YIZ Given: VS= SOV V=V=10V. Jz = 32MA Rz=0, Vin = 50V, R= 15 Rz=?, Pz(max)=?  $\frac{T}{R} = \frac{V_{in} - V_0}{R} = \frac{50V - 10V}{1K} = 40 \text{ mA}.$  $I = I_Z + I_L \implies I_L = I - I_Z = 40m - 32m$ I = 8mA  $R_{L} = \frac{V_{0}}{T_{1}} = \frac{10V}{8MR} = 1250\Omega$ Palmax) = IzVo = 32MXIOV Pr(max) = 320mw

15) A zerez diode hap a breakdown voltage og lov.

It is supplied flom a voltage source varying between 20-400. In Series with a Resiptance og 8208. Using an ideal zerez model obtain The Minimum & Maximum Zerez werent.

Given: R=820S. Vo=Vz=10V, Viemin)=20V, Vi(max)=40V.

Imin= Vi(min)-Vo R = 820S.

$$I_{max} = \frac{V_{i(max)} - V_{o}}{R} = \frac{40V - 10V}{820\Omega} = 36.585 \text{ mA.}$$

for ideal zener model,  $I_{Z}(min) = 0A$ .

$I_{L}(min) = 0A$ , when  $0|p$  transituals are open

$I_{max} = I_{Z}(max) + I_{L}(min)$

$I_{max} = J_{Z}(max)$

$\therefore I_{Z}(max) = J_{T}max = 36.585 \text{ mA.}$

$90V \frac{15}{2}$

$V_{o} = 10V$

HOV.

Applications of Diodes

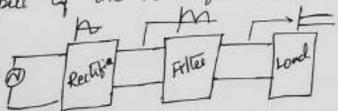

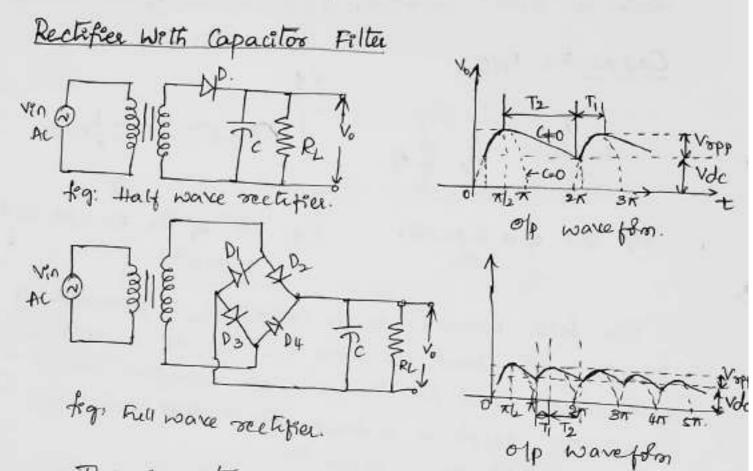

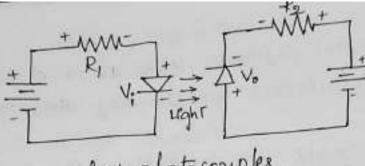

One of the nost important applications of diodes is vectification. other applications include clipping, Clamping, de voltage multiplication, and logic circuite. \* Reelification is the process of converting an ac voltage to de voltage i.e conversion of sinusoidal ac waveforme into single polarity half cycles. This can be accomplished by the use of rectifiers. filter and voltage segulator circuit. The rectified wave is smoothed by the use of capacitors to procen it into direct voltage.

an unwanted partion of a waveform.

(19)

- \* clamping white change the de level of a wavefolm without affecting the wave phape. i.e champing inwite shefts the pignal either to the the side of negative side of the axis.

- \* De voltage multiplicus are applied to change the level of a de voltage sonace to a desired high level

- \* Logic accusts produce a high & low ofp vlgs. depending upon the voltage levels at several ilp terminals.

- There are few seal time application & Diodes. If <u>Radio Demodulation</u>: Diode can be used in the demodulation of anythetide modulation (Ang) Sadio broadcasts. The Diode rectifier the Ang signal, leaving a signal whose average amplitude to the desired andro signal. The average value is extracted wing a simple fetter and fed into an andro Jeansduce, which generates pound.

- Over-voltage protection: Diodes are also used as protection devices for scapitive electronic components. Genalized doods called transient voltage supprenous are designed Eperifically for over voltage protection and can handle very large power prices for phore time periods.

- 3). <u>Limiter</u>: This circuit limits output proving to one diode drop soughly 0.7V. This drode kniters after used as ilp protection for high gain anytifies.

### Rectifiers:

Rectification: Reckfication is the process of converting alternating current (ac) to direct current (dc). <u>Rectifier:</u>

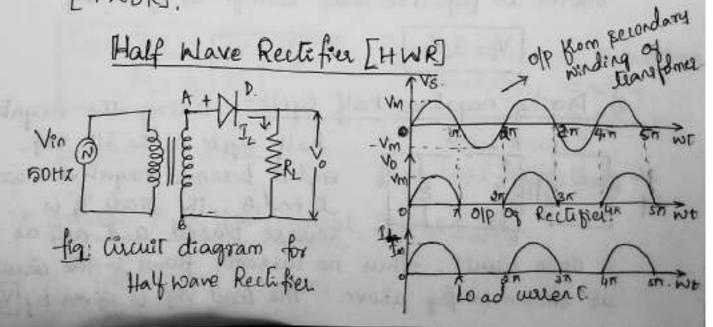

Rechtfree is a device -that converts ac (alternating hurrent) into de (direct current). Semiconductors diodes are used as rectifying elements. Rectifiers are classified as: V Half wave rectifier [HWR] &) Full wave rectifier [FWR] Full wave rectifier [FWR] Full wave rectifier and be built in two ways: V Full-wave vectifier nsing two diodes and a center tapped transformer → Fintre tapped full wave gectifier [CTFW] & Full-wave Rectifier [CTFW]

Pull-Wave Bridge sectifier using four diodes and an ordinary transformer→ Full Marce Bridge Rectifier. [FWBR].

In almost all the section in with, transformer are generally used for following purposes. I Etter to step up & step down the input vig. of To provide better is clation between AC supply and sectifier curit.

Hay wave rectifier circuit is as shown in grave above. It consigle of a pingle deade in peries we th load resistance. The ac voltage accors the secondary winding A & B changes polarities after half cycle.

Operation:

"During the half cycle:

AC DI A + DI VIL A

During the positive half lycle of the ac input vig. end A becomes populate with respect to end B. The deode Di is forward biased and acts as a short circuit, thus the current flows in the circultar Shown in fig. The load voltage is given by

Vo= JLRL & Vo= Vin

of During negative half cycle: During the negative JIE's z vo end A becomes negative wort AC reverse biased and acti as a open chuit, thus no warent flows in the circul as shown in fig above. The load vig is given by Vo=0

Scanned by CamScanner

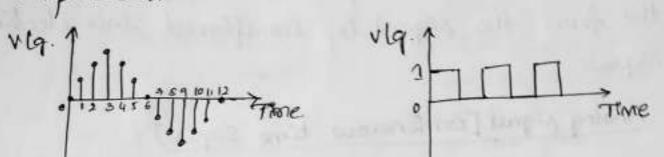

ter the Ip equation of the alternating secondary voltage is.

- The olp of the meeti fier is defined as

$$V_0 = \begin{cases} V_{m} Sinwt : 0 \le wt \le \pi \\ 0 ; \pi \le wt \le 2\pi. \end{cases}$$

The output waveform is expected to be a straight line but half wave sectifies gives output in the form of possifive sinusoi dal pulses. Hence the output is called pulsating dc.

The load current is given by.

$I_{L} = \int I_{m} Sinwt : 0 \le \omega T < \pi$   $\int O : \pi \le \omega T \le 2\pi$   $where \qquad I_{m} = \frac{V_{m}}{R_{L}} \quad V_{m} \Rightarrow peak value q the olp.$   $I_{m} = \frac{V_{m}}{R_{L}} \quad where. \quad R_{S} \Rightarrow Resistance og transformo secondorry winding vol > Dynamic vesistance og transformo secondorry vinding vol > Dynamic vesistance og transformo secondorry vesistance og tra$

$$= \frac{1}{2\pi} \left[ \int_{0}^{\pi} T_{m} Sinwt \, dwt + \int_{\pi}^{\pi} \sigma \cdot dwt \right]$$

$$= \frac{1}{8\pi} \left[ \int_{0}^{\pi} T_{m} Sinwt \, dwt \right]$$

$$= \frac{1}{8\pi} \left[ -i0\betawt \int_{0}^{\pi} \right] = -\frac{T_{m}}{2\pi} \left[ -i - 1 \right]$$

$$= -\frac{T_{m}}{8\pi} \left[ -\frac{\pi}{2} \right]$$

$$\frac{1}{9dc} = \frac{T_{m}}{\pi}$$

$$\frac{1}{8\pi} \left[ -\frac{\pi}{2} \right]$$

$$\frac{1}{9dc} = \frac{T_{m}}{\pi} \left[ -\frac{\pi}{2} \right]$$

$$\frac{1}{9dc} = \frac{T_{m}}{\pi} \cdot R_{L}$$

$$= \frac{T_{m}}{\pi} \cdot R_{L}$$

$$= \frac{T_{m}}{\pi} \cdot R_{L}$$

$$= \frac{V_{m}}{\pi} \cdot R_{L} \quad \left[ \cdots T_{m} = \frac{V_{m}}{R_{L}} \right]$$

$$\frac{1}{9dc} = \frac{V_{m}}{\pi}$$

$$\frac{1}{8} \frac{N_{ms} \text{ value } q \text{ Load current } (T_{rms}):$$

$$T_{rms} = \sqrt{\frac{1}{2\pi}} \int_{0}^{\pi} T_{L}^{2} \cdot dwt.$$

$$= \left[ \frac{1}{2\pi} \int_{0}^{\pi} T_{m}^{2} Sin^{2}wt \, dwt + \int_{0}^{\pi} \sigma \cdot dwt \right]^{1/2}$$

$$= \left[\frac{\pi h}{2\pi}\int_{0}^{\pi} \operatorname{Stdwcdwt}^{1/2}\right]^{1/2}$$

$$= \left[\frac{\pi h}{2\pi}\int_{0}^{\pi} \operatorname{Stdwcdwt}^{1/2}\right]^{1/2}$$

$$= \left[\frac{\pi h}{2\pi}\int_{0}^{\pi} \left[\frac{-\cos 2\omega c}{2} d\omega \right]^{1/2}$$

$$= \left[\frac{\pi h}{2\pi}\left[\frac{\pi}{2} - d\right] - \left[\frac{\sin 2\pi}{4} - \frac{\sin 2\omega c}{4}\right]^{1/2}\right]^{1/2}$$

$$= \left[\frac{\pi h}{2\pi}\left[\frac{\pi}{2}\right] - d - \left[\frac{\sin 2\pi}{4} - \frac{\sin 2\omega c}{4}\right]^{1/2}\right]^{1/2}$$

$$= \sqrt{\frac{\pi h}{2\pi}\left[\frac{\pi}{2}\right]} = \sqrt{\frac{\pi h}{4}}$$

$$\frac{\pi h}{2}$$

$$\frac{\operatorname{Rms} = \frac{\pi h}{2}}{\operatorname{Rms} \cdot R_{L}}$$

$$= \frac{\pi h}{2} \cdot R_{L}$$

$$= \frac{\operatorname{Rms} \cdot R_{L}}{\operatorname{Rms} = \frac{\pi h}{2}}$$

$$\frac{\operatorname{Rms} = \frac{\operatorname{Rms}}{2} \cdot R_{L}}$$

$$= \frac{\operatorname{Rms}}{R_{L} \cdot 2} \cdot R_{L}$$

$$= \frac{\operatorname{Rms}}{R_{L} \cdot 2} \cdot R_{L}$$

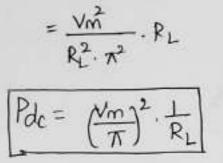

$$= \left(\frac{\operatorname{Rms}}{\pi}\right)^{2} \cdot R_{L} = \frac{\pi h}{\pi^{2}} \cdot R_{L}$$

$$= \left(\frac{\operatorname{Rms}}{\pi}\right)^{2} \cdot R_{L} = \frac{\pi h}{\pi^{2}} \cdot R_{L}$$

6) Ac Output power (Pac)  $P_{ac} = \overline{I_{Rms}} \cdot R_L$  $P_{ac} = \left(\frac{I_m}{2}\right)^a \cdot R_L$

# => Rectifier Efficiency.

The efficiency of rectifiency is defined as the ratio of the old power to the Istal anount of ilp power supplied to the circuit.

$$\eta = \frac{Pdc}{Pac.}$$

$$= \frac{\frac{Jm}{R^2} \cdot R_L}{\frac{Tm}{4} \cdot R_L} = \frac{\frac{1}{R^2}}{\frac{1}{4}}$$

$$= \frac{\frac{1}{R^2}}{\frac{1}{4}}$$

M= 40.6.1. Indicates that, under the most Ideal Londitions, only 40.6.1 of the a.c. "Ip power is converted into de power in the load. The remaining eripts as a c power.

## 8> Repple Factor

The repidual pulsation in the direct current from a sectifier is called a sepple. A measure of the proothness of the d.c olp of a rectifier ix called a supple factor. J. Ripple factor indicates how successfully a circuit is in converting the a.c to d.c. This is defined as,

Ripple factor = 7= effective (r.m.s) value q ac component average d. d. c components.

The requirement of a rectifier ip to minimize its sepple factor (sepple content). This is achieved by introducing a filter in the sectifier ofp. Thus, a filter converts a pulsating old from a vertilier into a very steady state die output & it filtre our & proothers out the pulsations at the output.

If Iac is the effecting value of the a.c components, then the total load current is the RMS Value of the iL is,

VC9/ Share and Deparent

(23)

amount of a.c present in the olp is 121.1. of the d.c voltage.

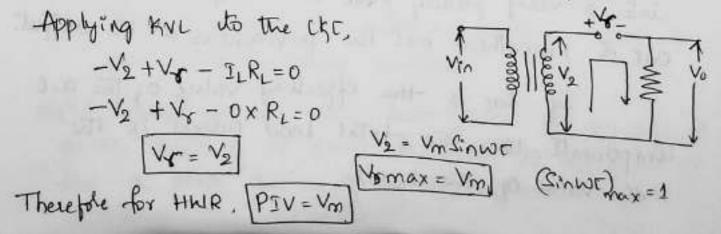

9) Peak Inverse Voltage [PIV]

PIV is the maximum voltage access the diode, when the diode is reverse biased.

Scanned by CamScanner

10> Voltage Regulation

Regulation à defined as the variation in DC Output voltage as a function of DC current.

If the Regulation is zero then et is edeal rectifier but in actual practice

$$R_{\rm equilation} = \frac{R_{\rm S} + R_{\rm F}}{R_{\rm L}} \times 100$$

#### Advantages :

- 1. The circuit is simpler and requires only one diode. 2. PIV is only Vm.

- 3. Centre tap transformer is not neccessary.

#### Disadvantages:

- 1. Repple factor J= 1211/ is too high.

- &. Effectency to very low about 400-1. but practice value is still less.

- 3. Low transformer utelization factor = 0.287.

- A. Because of all these dependion tages HWR is not used as power sectifier.

Note: Transformer utilization factors [TUF]: It is defined as the ratio of dc power delivered to the load to the ac power rating of the transformer.

## Full-Wave Rectifier

The disadvantages of a half wave sectifier are seduced & eliminatedos by the use of another diode. Here both the half cycles of the input are utilized and is used with the centre lapped transformer.

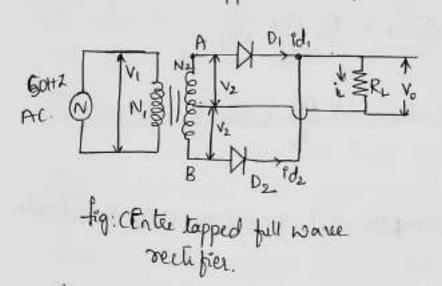

A full wave rectifier viewir with two diddes and a cente-tapped teansplaner is as shown in fig.

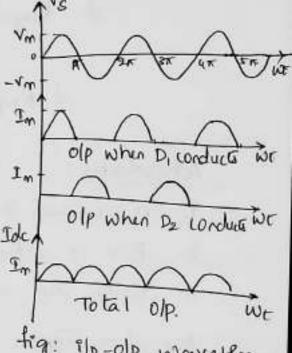

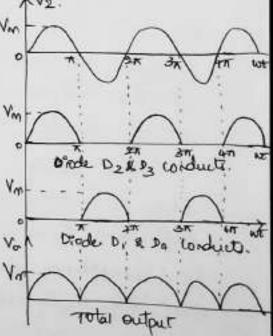

When the slp as supply is Total olp. In switched on, the ends A & B Qy fig: ilp-olp workerform the transformer secondary becomes the Q Full name & -ve alternatively.

#### operation:

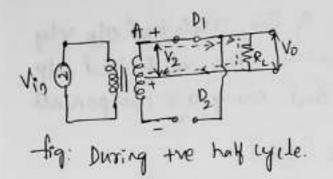

During the half cycle: During the half cycle of the ac input voltage, end A becomes the with respect to end B, the diade 'Di' is for word braped and conducts while the drade D2 is reverse braped and acts as open church and conducts while the other drade D2 is reverse braped and acts as an open circuit and will not conduct as shown in fig below.

The Diode Di supplies the load merent. The convertional unreal flow a theorigh Di load resistor Re and the upper half of the secondary winding as shown by the dotted arrows.

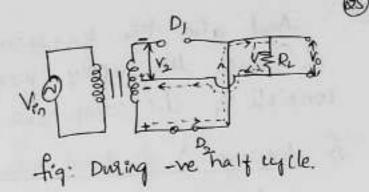

## During the -ve half Cycle:

During the -ve half cycle of the input acrig end A becomes -ve with respect to end B. the diade 'D' is forward biased and conducts while the diade 'D' is reverse biased and acts as open cacuit and will not conduct as shown in fig above. The diade Dz supplies the load current. The conventional current flow is through diade Dz. load resistor R. and the lower half of the Secondary winding as shown by the dotted lines in the figure above.

At seen from the two figures above, the merent in the load R is in the same direction for both half wycles of at ilp vig.

For both the half cycles the means flows through the load in the same disection there we get two half cycles for one complete input signal. And also the frequency of the sectified ofp vig is twice the supply frequency. The sectified ofp consists of d.c. components and many a.c. components.

## 1) Average & de Load averant [Ide]

Considering one cycle of the Load current  $I_L$  from 0 to  $\pi$  to obtain the average value which

is de value of load current.

$$dc = \frac{1}{\pi} \int_{0}^{\pi} I_{L} d\omega r$$

$$= \frac{1}{\pi} \int_{0}^{T} I_{m} Sin \omega r d\omega r.$$

$$= \frac{\underline{T}_{m}}{\underline{\pi}} \left[ -\log \operatorname{NE} \right]_{0}^{n}$$

$$= \frac{\underline{T}_{m}}{\underline{\pi}} \left[ -\log \overline{\pi} - (-\log \varepsilon) \right] = \frac{\underline{T}_{m}}{\underline{\pi}} (2)$$

$$\frac{1}{\sqrt{\pi}} = \frac{2\underline{T}_{m}}{\overline{\pi}}$$

Average dc load voltage: [Vdc]

Vdc = Idc·RL

= ØIm RL = QVm RL

Td c = ØIm The equation of the

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1}{2} \cdot S_{1} \lambda \otimes t \cdot d\omega t$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega t \cdot d\omega t)}{2}$$

$$= \sqrt{\frac{1}{\pi}} \int_{0}^{\pi} \frac{1 - (o_{\beta 1} \omega t \cdot d\omega t \cdot d\omega$$

\*

D2

# Advantages of FWR.

1) The efficiency is twice that of the i.e 81.21. 2) The sipple factor is much less than that of the R 3) The dc olp subject voltage and load current value are twice than the R.

H} harge de output

5) Full 1001. og the enpur is utekned

## Disadvantages of FWR.

> PIV of the diade is higher.

et cost of centre tap teansformer is higher.

3) output voltage is holy of the secondary voltage.

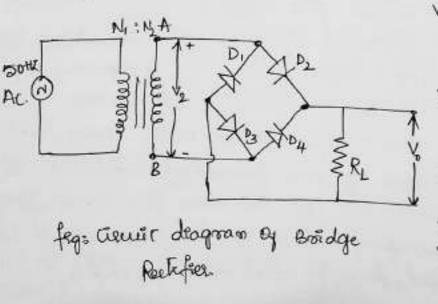

## FULL WAVE BRIDGE RECTIFIER.

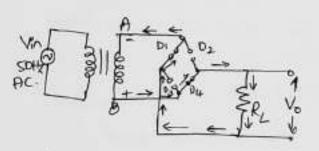

Boidge Rectifier is the most frequently used circuit for electronic doc power supplies. Form Diodes are used but the transformer used is not centre tapped and gives output of V2. The incurr diagram for Bridge rectifier and the sespective wavefilms are as shown in fig below. N2.

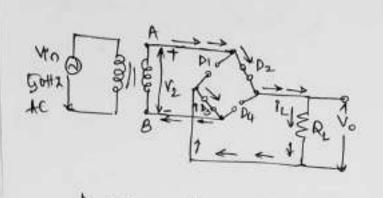

During the half cycle:

Diviting the half cycle of the ip ind A becomes the north respect to end B. This makes Diode D2 & D3 forward brased and the diodes D, & D4 severse brased. These fole only diodes

Bits by conducts during the we half will by the input. The conventional current flows through the load resistance Re as shown in figure producing the drop awars Re. During -ve half cycle

During -ve half whele of the ip end A becomes -ve with respect to end B. This makes Drode D, & D4 forward biased and the drodes D2 & D3 reverse

biased. Therefore only deader D, & Dy conducts during the -ve half cycle of the input. The conventional werent flows through the load seriptance R, a shown in fig. producing the deep accepts the R.

For both the half cycles the water flows through load in the same direction. Hence we get two half cycles for one complete input signal. i.e. The prequency of the ofp is double that of the ip supply prequency.

The bridge circuit transformer needs only half the secondary turns of the transformer compared to full wave seelifier circuit for the same of ofp woltage. ie transformer secondary line - to - kne vig should be one half that used for the full wave sectifier. Advantages of FWBR: 1). The need for centre tapped transformer is eliminated 2). The piv is only Vm. 2). The piv is only Vm. 3). The transformer is less costly.

Disadvantages & FWBR: IT It requires force diodes, causing an additional voltage deep that reduces the ofp vlg.

Applications of Rectifiers: 17 In Power supply circuite.

a) In sectifier type meter to convert ac voltage to be measured to DC.

comparision of Rectifier circles to.

| parameter                          | HWR                                               | FWR                                                     | FNBR.                                                                |

|------------------------------------|---------------------------------------------------|---------------------------------------------------------|----------------------------------------------------------------------|

| 1) Peak voltage                    | Vm=V2 V2<br>= V2 x Vs                             | $V_m = \sqrt{2} V_2$ $V_m = \sqrt{2} \times V_3$        | $V_m = \sqrt{2} \cdot \sqrt{2}$ $= \sqrt{2} \cdot \sqrt{5}.$         |

| 1> Peakloadcussent<br>[Ideal].     | $\mathcal{I}_{m} = \frac{V_{m}}{R_{L}}$           | $I_m = \frac{V_m}{R_L}$                                 | $T_m = \frac{V_m}{R_L}$                                              |

| s) Peakload Cuseenr<br>[prac Rial] | $\underline{T}_{m} = \frac{V_{m}}{R_{f} + R_{L}}$ | $\mathcal{I}_m = \frac{V_m}{R_f + R_L}$                 | $\mathcal{I}_{m} = \frac{V_{m}}{\mathcal{R}_{f} + \mathcal{R}_{L}}$  |

| A) DC Load Weenr                   | $I_{dc} = \frac{I_m}{\pi}$                        | $I_{dc} = \frac{\theta I_{m}}{\pi}$                     | $I_m = \frac{2Im}{\pi}$                                              |

|                                    | $I_{de} = \frac{V_{00}}{(R_{g}+R_{z}) \cdot \pi}$ | $Id_{c} = \frac{2 \cdot Vm}{(R_{f} + R_{c}) \cdot \pi}$ | $I_{dc} = \frac{2 \cdot V_{m}}{(2R_{f} + R_{f}) \cdot \overline{n}}$ |

| Ac load cuerent                    | I <sub>Rms</sub> = <u>Im</u>                      | $T_{Rms} = \frac{T_{cm}}{\sqrt{2}}$                     | Jems = Im<br>V2                                                      |

| 67 AC Ilp power<br>(Toleal)        | Pac = JRms . RL                                   | Pac= I Ams RL                                           | Pac=Jonns. RL                                                        |

#Ac ilp po usee

[practical]Pac =

$$I_{oms}^{2}$$

( $R_{L} + R_{f}$ )Pac =  $I_{rms}^{2}$  ( $R_{L} + R_{f}$ )Pa

#### Problems.

In a full wave beidge sectifies, the transformer Recordany voltage is loosinwt. The forward resistance Q Cach deode is 252 and the load resistance is 9502 Calculate & D.c olp vlg & Repple factor 25 Efficiency & rechtscation \* PIV Soln: Given:  $N_S = 100Sinwt$ ,  $R_I = 252$ ,  $R_L = 9502$   $V_S = V_2 = V_{00} Sinwt$  = Wm = 100.  $I_{00} = \frac{Vm}{R_F + R_L} = \frac{100}{(R \times 25) + 950} = 0.1A.$  $I_{0c} = \frac{QI_{00}}{T} = \frac{Q \times 0.1}{T} = 0.063A.$

$$\begin{array}{l} 17 \quad \forall \partial c = \overline{I} dc \ R_{L} = 0.063 \times 950 = 59.85 \vee \\ 37 \quad \sqrt{I} = \sqrt{\left(\frac{Tems}{Idc}\right)^{2} - 1} = \sqrt{\left(\frac{0.09709}{0.063}\right)^{2} - 1} \qquad T_{Rms} = \frac{\overline{J}m}{\sqrt{2}} \\ \hline \overline{V} = 0.0448 \qquad \qquad = \frac{0.1}{\sqrt{2}} = 0.07074 \\ 37 \quad Pdc = \overline{I} dc^{2} \ R_{L} \qquad Pac = (\overline{I}_{Rms})^{2} (2R_{I} + R_{L}) \\ = (0.063)^{2} \times 950 \qquad = (0.0707)^{2} (2\times25 + 950) \\ Pdt = 3.85 & Pac = 5 & N \\ \gamma = \frac{Pac}{Pdc} \times 100 \\ = \frac{5}{3.85} \times 100 \\ \hline \overline{V} = \overline{V} = \sqrt{100} \\ \hline PJ = \overline{V} = V_{m} = 100 \end{array}$$

e) In a two deode FWR CGT. the voltage a work

lach half of the transformer secondary is toor.

The load resistance is 9500 and each deode has a

forward resistance of 500. Find the load current

and the rms value of the Input current.

Soln: Given :

$$V_S = 100$$

.  $R_f = 500$ .  $R_L = 9500$

\*  $V_m = \sqrt{2} \times V_S = \sqrt{2} \times 100 = 141.42v$

#  $I_m = \frac{V_m}{R_f + R_L} = \frac{141.42}{950+50} = 0.141A.$

#  $I_{RmS} = \frac{Im}{\sqrt{2}} = \frac{0.141}{\sqrt{2}} = 0.0997A.$

#  $I_{dc} = \frac{2Im}{\pi} = \frac{2\times0.141}{\pi} = 0.090A.$

3) A Bridge sectifier is driving a load substance of

DOD. It is driven by a sonare voltage of 2800 50Hz

Neglecting drode substatione - calulate

is the quency of alp waveform

Solar Given:

$$R_{L} = 100\pi \cdot V_{S} = 230^{\circ} \cdot f_{1n} = 50HZ$$

.

$V_{m} = \sqrt{2} \times V_{S} = \sqrt{2} \times 230 = 325^{\circ}$

$V = \sqrt{2} \times V_{S} = \sqrt{2} \times 230 = 325^{\circ}$

$V = \sqrt{2} \times V_{S} = \sqrt{2} \times 230 = 325^{\circ}$

$V = \sqrt{2} \times V_{S} = \sqrt{2} \times 230 = 325^{\circ}$

$V = \sqrt{2} \times V_{S} = \sqrt{2} \times 230 = 325^{\circ}$

$V = \sqrt{2} \times V_{S} = \sqrt{2} \times 325} = 206.9^{\circ}$   $V = \sqrt{206.9^{\circ}}$

$= \sqrt{2} \times \frac{2}{\pi} = \frac{2\times 3.25}{\pi} = 2.06^{\circ}$

$T_{m} = \frac{\sqrt{m}}{\pi} = \frac{325}{\pi} = 2.06^{\circ}$

$T_{m} = \frac{\sqrt{m}}{\pi} = \frac{325}{100} = 3.26$

$= \sqrt{2} \text{ of } \text{ Bequency} = 2 \text{ for } 2\times50^{\circ} = 100\text{ Hz}.$

$= \sqrt{2} \text{ of } \text{ Bequency} = 2 \text{ for } 2\times50^{\circ} = 100\text{ Hz}.$

$= \sqrt{2} \text{ of } \text{ Bequency} = 2 \text{ for } 2\times50^{\circ} = 100\text{ Hz}.$

$= \sqrt{2} \text{ or } X \text{ Ior A set fight. The input is form  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is form  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{\circ}$

$= 100^{\circ} X \text{ Ior A set set fight. The input is good  $30-0-30^{$$$$$$$$$$$$$$$$$$

\*

$$P_{dc} = (I_{dc})^2 R_L = (0.2455)^2 \times 100 = 6.027W$$

\*  $P_{dc} = I_{oms} (R_L + R_L) = (0.272)^2 (10+100) = 8.177W$

\*  $I_{oms} = \frac{I_m}{\sqrt{2}} = \frac{0.3856}{\sqrt{2}} = 0.2724.$

\*  $1.97 = \frac{P_{dc}}{P_{ac}} \times 100$

$= \frac{6.027W}{8.177} \times 100 \quad [9]_{1.} = 73.61$

$1.9 \text{ Regulation} = \frac{R_L}{R_L} \times 100 = \frac{10}{100} \times 100 = 10.$

5) A diade with  $V_P = 0.9V$  is connected as a half worke sectifier. The load seriptionie is 60051 and the (2005) act the old seription of the peak of the old seription of the peak several voltage.

$O_{D} = G^{1} \times 9 = 0.7V.$   $R_L = 600.$   $V_S = 24V.$

\*  $V_m = \sqrt{2} \times V_S = \sqrt{2} \times 24 = 33.941V.$

#  $I_m = \frac{V_m - V_P}{R_L} = \frac{33.941 - 0.7V}{600} = 55.4018 \text{ mA.}$

\*  $P_{ac} = V_0 = I_m R_L = 65.401 \times 10^3 \times 600$

$(V_0 = V_m - V_P = 33.94V.$

S

6. The input to a half have settifier is v=200sin 50t

If

$$R_{L} = 1K$$

and fillward resplance of the diode is

Solohnit find

is do current through the diode

s) a.c. d 2.ms value of the current through the (kt.

s) The d.c olp viz.

A) The a.c. Ilp power.

Solo: Given:  $V_{T} = 200 \sin 50t$ ,  $R_{L} = 1K$ ,  $R_{f} = 500st$

$V_{T} = Vm \sin 0t$

$V_{T} = 200$

Peak value of load current  $Tm = \frac{Vm}{R_{L} + R_{L}} = \frac{200}{50 + 1K}$

$V_{T} = \frac{Tm}{R} = \frac{190 \times 10^{3}}{R}$

$Tm = 0.19$

$Pac = 60mA$

$M = \frac{Tm}{2} = \frac{190}{2} = 95mA$

$M = A.c. Ilp power, fac$

$Pac = (Eams)^{2} \times (R_{L} + R_{L})$

$Pac = (1dc)^{2} \times R_{L}$

$= 60mA \times 1K$

$Vdc = 60 volls$

$Pdc = (Tdc)^{2} \times R_{L}$

$= (0.06)^{2} \times 1000$

$Pdc = 3.6W$

$V = 34.9$

An a.c vlg of 25V is applied in series with a <sup>3</sup> sikion diode and a load sesiptance of 10005. If the floored sesistance of the diode is los. Find the peak current through the diode and peak ofp vlg.

<u>Soln</u>: Given:  $V_{ms} = 25V$ ,  $R_L = 10000$ ,  $R_f = 10f2$  $V_m = \sqrt{2} \times V_{ms} = 1 + 14 \times 25 = 35.35V$ .

> Peak value of the current, Im = Vm Rf+RL

> > = 35.35 = 35mA. 10+1000

$$Vdc = Idc \cdot R_{L} = \frac{Jm}{\pi} \cdot R_{L} = \frac{0 \cdot 035}{\pi} \times 1000$$

$$Vdc = 11 \cdot 14V$$

$$Peak \ olp \ voltage = Im \times R_{L} = 0.035 \times 1000$$

$$Vm = 35V.$$

Soln: Given: VS = 50V, RL= 15, Rf = 2052

The a.c & Rms value og a.c vlg aude each Secondary nalf is 504.

. Ym = V2 × 50 = 70.7V.

\*

$$I_m = \frac{V_m}{R_f + R_L} = \frac{70.7}{20.1000} = 69.3 \text{ mA}$$

\*  $I_d$ . de value og wærent through  $R_L = \frac{9.5m}{\pi}$

$I_d = 44.12 \text{ mA} \times 16$

$I_d = 44.12 \text{ mA} \times 16$

$I_d = 44.12 \text{ mA} \times 16$

$V_d = 46.04$

$V_d = 46.04$

a)  $Vdc = Idc \times R_L = (180 \times 10^3) \times 500$ Vdc = 90V

A) PIV accoss non-conducting diodes = Vm = 155.56 V.

10>. A HWR DC output vig at no load is found to be 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 0.4A is drawn from 12v. when full load werent of 0.4A is drawn from 0.4A is drawn from

Soln: Givens VNL=12V . VFL=10V.

o/s Regulation =

$$\frac{V_{NL} - V_{FL}}{V_{FL}} \times 100$$

=  $\frac{12 - 10}{10} \times 100$

=  $\frac{90}{10}$

117. For a Sinupoidal og 100 Sin 210t volte is applied to Full wave bridge rectifier. Determine the efficiency if R1 = 10002 and R1 = 2K2. Consider deoder with forward resistance R4 = 1052 are used.

Soln: Given: Vs=100Sin 210t Rg=10.12 Vm=100V.

$$\begin{array}{l} (\underline{a},\underline{k},\overline{i}) \quad R_{\underline{j}} = 1000 \, \Omega \\ & \eta = \frac{0.812}{\left[\frac{\sqrt{2}}{R_{L}} + 1\right]} \times 100 \, 4. \\ & \left[\frac{\sqrt{2}}{R_{L}} + 1\right] \\ & \eta = \frac{0.812}{\left[\frac{\sqrt{2}}{1000} + 1\right]} \times 100 = 79.6 \, 4. \\ & \eta = \frac{0.812}{\left[\frac{\sqrt{2}}{1000} + 1\right]} \times 100 = 79.6 \, 4. \end{array}$$

$$\eta = \frac{0.812}{\left[\frac{0.812}{R_1} + 1\right]} = 80.39.16$$

07

#### FILTERS

The main function of a filter is to reduce & eliminate noise from the information. In the rest fier circuit it is used to minimize the sipple content in the sectified ofp.

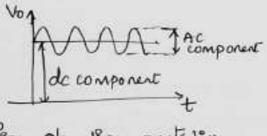

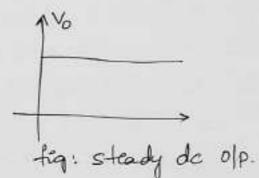

Need: The olp of the rectifier circuit is pulsoling DC. Such an olp has a dic components and some a.c components called sipples. such an output is not of much use for driving sophisticated electionic devices and circuits. which sequires a very steady dc olp, which should be almost as smooth as the dp from a battery. such an olp may be obtained by introducing filter.

fig: olp from sectifier.

Definition: The filter may be defined as. It is a device, which removes AC components of the rectifier output but allows the DC component to reach the load of it is a circuit, which converts pulsating output of the rectifier into a steady DC level.

Filtys should be installed blue the sectifies blue the sectifier and the load as shown in fig above

Type of felters: i) capacetos stric-felter i) capacetos strict felter & x section. i) Inductor is clic felter & x section. out of all these 'force type' of filters. Capacetos out of all these 'force type' of filters. Capacetos felter is most commonly used because of the low cost

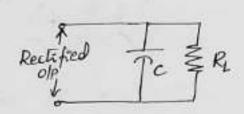

Capacitor Filte:

fig: chr q a capacetor filte

fig: olp of the Rectifier worth capacetor.

The fille consists of a capacitor a connected in parallel with load resistance RL. The olp is available across the load resistor. The off waveform shows that the sipple is reduced to a great extent due to the addition of capacitor.

we know that capacitor stole energy. They can take a charge and then later delivers that charge to the load with the increase in rectifier vlg, the capacitor is charged and onde current is supplied to the load later when the sectifier ofp decreases the capacitor discharger through the load and the vlg access the parallel combination of R and c decreases. This decrease is only slight because the next vlg peak comes immediately and charges the capacitor This process is separated again and again. and hence the Repple is seduced

The factors which determines the effectiveness of capacitors are & Size of the capacitor & The value of the load & The time blue the pulsations.

The capacitor in both the investile are placed access the rectifies of Ri i.e Load. The pulsating DC of the rectifies is applied access the capacitor. As rectifies voltage inteases it charges the capacitor towards Vm because initially capacitor acts as a short. At the end of quarter cycle (TH2) it is charged to peak value Vm of the rectifies vig as shown in fig above once capacitor voltage reaches Vm diode is reverse brased where anode of diode is positive but less then Vm hence diode is reverse brased and stops conducting. Now capacitor

discharges through the load and the vollarge anoss it deveaper. Capacitos discharges until the Input voltage is less than capacitor voltage. Once the input voltage is greates than capacitor voltage the diode is forward brazed and capacetor charges to Vm. and some cycle repeats.

The expression for supple factor (7) is given by.

T= \_\_\_\_ > for thalf ware rectifier &J3fC.RL E Lenn

where,

Re- Load reliptance f - Frequency C-> capacitance

DC output voltage

$$Vdc = Vm - \frac{Vrpp}{2}$$

$$l_c = V_m - \frac{Idc}{2fc}$$

$Idc = \frac{Vdc}{RL}$

$$Vdc = Vm - \frac{Vdc}{2fR_{1}C}$$

for full wave rectifier.

& Vac

$$V\partial c = Vm - \frac{Idc}{4fc}$$

$$V\partial c = \frac{Vm}{1 + \frac{1}{4fR_{1}c}}$$

#### Problems

17 A full wave sectifies using centre topped transformes Euppher a resignice load of IKA. The teansformer Secondary end to end voltage is GOV and at SOHZ. The feltu capacitance is 500 µF. Calculate a) Ripple factor by output resistance of the filter (Re) e) Vdc dy Idc et 1/0 segulation.

Soln: Given: RL= IK, C= 500 MF. Voms= 60V. [end to end]. . Vans= 30V.

$$= \frac{1}{4\sqrt{3}R_{1} \cdot C \cdot f} = \frac{1}{4\sqrt{3}\times1\times10^{3}\times500\times10^{5}\times50}$$

$$= 0.0050$$

by old resistance of the filter Ro

$$R_0 = \frac{1}{4fc} = \frac{1}{4x50x500x10^6} = 10.02$$

$$dr = \frac{Van}{1 + R_0/R_L} = \frac{42.42}{1 + \frac{10}{1K}} = 42V$$

Vm= V2 × Voms = V2 × 30 = 42.42V

$$\frac{dy}{Idc} = \frac{Vdc}{R_L} = \frac{H_2V}{IK}$$

$$\boxed{Idc = H_2mA}$$

$$ey \cdot 10 \quad Regulation = \frac{R_0}{R_L} \times 100 \cdot 1.$$

$$= \frac{10}{I \times 10^3} \times 100$$

$$= 1 \cdot 1.$$

| 2) Design a full wave sectifier with c-feller for the 3                      |

|------------------------------------------------------------------------------|

| following specifications: Ripple factor < 0.06.                              |

| ofp de vig=35V, Maximum load werent=260mA.                                   |

| Soln: Given: Vdc=35V. Idc=250mA. J=0.06                                      |

| Assuming, f= 50HZ                                                            |

| $R_{L} = \frac{Vdc}{Idc} = \frac{35V}{260mA} = 140.52$                       |

| $\nabla = \frac{1}{4\sqrt{3}fCRL}$                                           |

| $C = \frac{1}{1} = \frac{1}{1} = 343.66  \text{mF}.$                         |

| 453 fre 453×50×140×0.06                                                      |

| Vm = Vdc + Idc                                                               |

| 4fc                                                                          |

| = 35+ 250mA = 6 = 38.53V                                                     |

| = 35 + 230111<br>4× 50× 343.66×10 = 38.53V                                   |

| Vm=J2Voms                                                                    |

| $V_m = \frac{V_m}{\sqrt{2}} = \frac{38.53V}{\sqrt{2}} = 27.3V$               |

| 3). A full wave bridge rectifier is supplied from the                        |

| transformer secondary voltage of 100%. Calculate                             |

| the dc old voltage and peak Inverse voltage of the                           |

| diode employed.                                                              |

| Soln: Given: Verms)= 100V, Vdc=?, PIV=?                                      |

| $Wm = \sqrt{2} \cdot V_{2ms} = \sqrt{2} \times 100 \qquad \text{w piv} = Vm$ |

| $V_m = 141.42V$<br>$P_{IV} = 141.42V$                                        |

| * $Vdc = \frac{2\Psi_m}{\pi} = \frac{2 \times 14 \cdot 142}{\pi} = 90 \vee$  |

|                                                                              |

Hy Draw the vacuus dragton of a full work settifier

with capacitor filter the vacuus uses a capacitor

of 1000 µF and provides a de load current of 500 mm

at 24 stipple. Answere

$$f_{\pm} = 50 \text{ Hz}$$

calculate:

1) D.C output voltage s) peak sec Effective lage and

1/2 seque Ron.

Solar Given:  $L = 1000 \text{ µF}$ ,  $I_{dc} = I_{L} = 500 \text{ mm}$ ,  $T = 0.02$ .

$f_{\pm} = 50 \text{ Hz}$

$T = \frac{1}{\text{ HJ}_{3}R_{L}Cf}$

$T = \frac{1}{\text{ HJ}_{3}R_{L}Cf}$

$R_{L} = \frac{1}{\text{ HJ}_{3}} \frac{1}{\text{ HJ}_{3}} \frac{1}{\text{ X} = 502 \times 1000 \times 10^{5} \times 0.02}$

$R_{L} = 1144.34 \text{ m}$

i) D.C off Vlg.

$V_{dc} = I_{dc} R_{L} = 500 \times 10^{3} \times 144.34 \text{ s}$ .

$V_{dc} = I_{dc} R_{L} = 500 \times 10^{3} \times 144.34 \text{ s}$ .

$V_{dc} = T_{dc} R_{L} = 500 \times 10^{3} \times 144.34 \text{ s}$ .

$V_{dc} = \frac{1}{\text{ H} L} \frac{1}{\text{ Hf} C}$

$N_{m} = \frac{1}{21.17 \text{ J}}$

$N_{m} = \frac{1}{21.17 \text{ H}} \frac{500 \times 10^{3}}{\text{ Hf} C}$

$N_{m} = \frac{1}{21.17 \text{ H}} \frac{500 \times 10^{3}}{\text{ Hf} C}$

$N_{m} = \frac{1}{21.17 \text{ H}} \frac{500 \times 10^{3}}{\text{ Hf} C}$

$N_{m} = \frac{1}{34.64 \text{ V}}$

$N_{m} = \frac{1}{82} \times 100 \text{ f} \frac{50}{144.34 \text{ H}}$

$N_{m} = \frac{1}{2.13 \text{ H}} \frac{500 \times 10^{3}}{\text{ Hf} C}$

$N_{m} = \frac{1}{2.13 \text{ H}} \frac{500 \times 10^{3}}{\text{ Hf} C}$

$N_{m} = \frac{1}{34.64 \text{ V}}$

$N_{m} = \frac{1}{82} \times 100 \text{ f} \frac{50}{144.34 \text{ H}}$

$N_{m} = \frac{1}{82} \times 100 \text{ f} \frac{50}{144.34 \text{ H}}$

$N_{m} = \frac{1}{82} \times 100 \text{ f} \frac{50}{144.34 \text{ H}}$

$N_{m} = \frac{1}{82} \times 100 \text{ f} \frac{50}{144.34 \text{ H}}$

$N_{m} = \frac{1}{82} \times 100 \text{ f} \frac{50}{144.34 \text{ H}}$

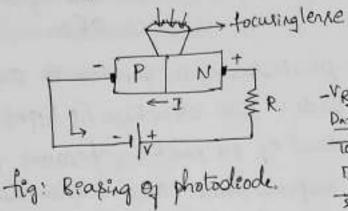

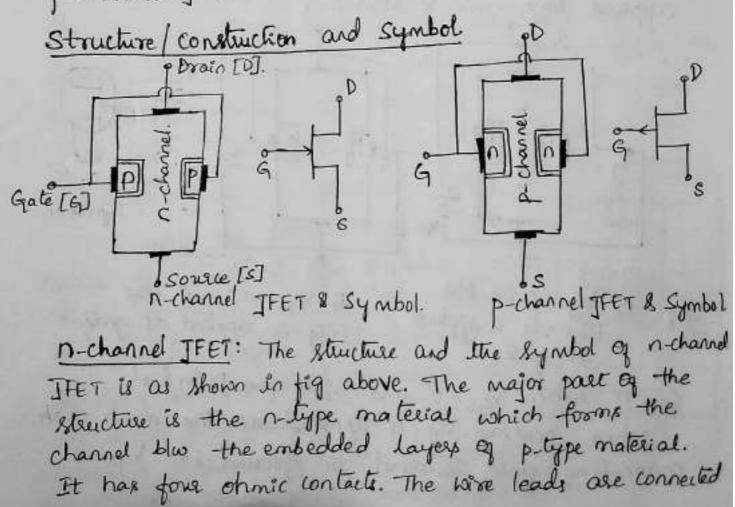

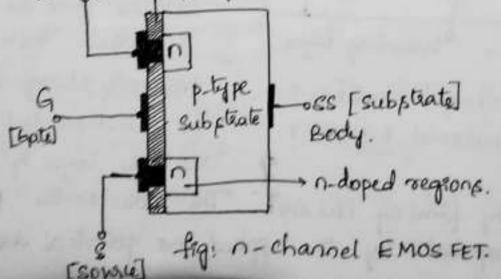

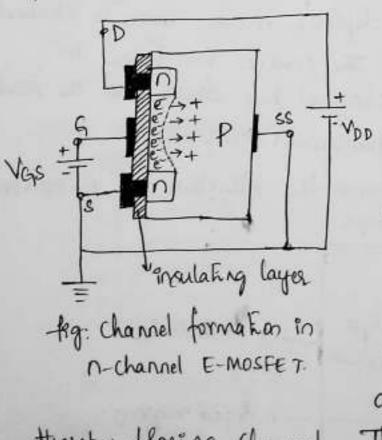

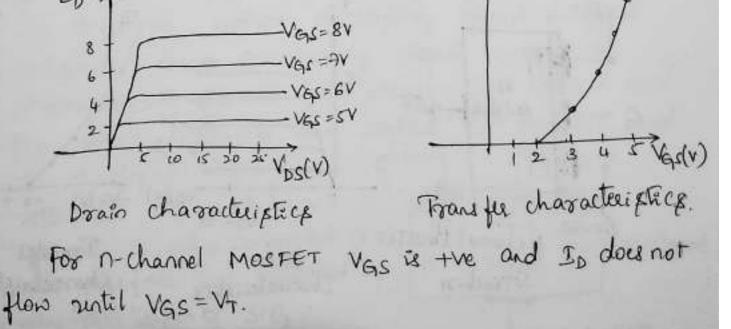

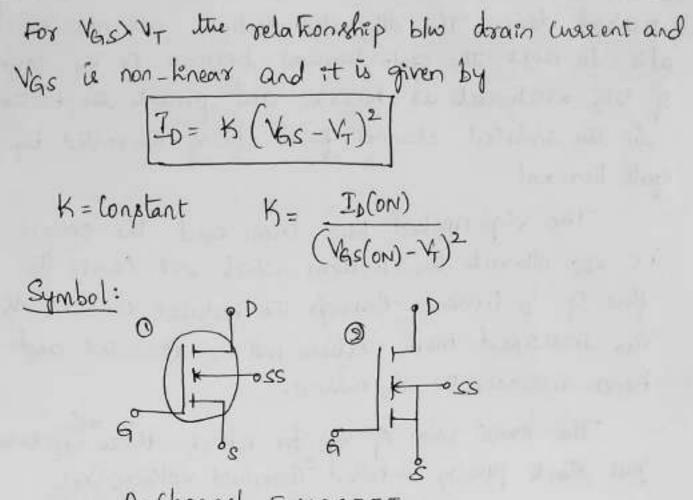

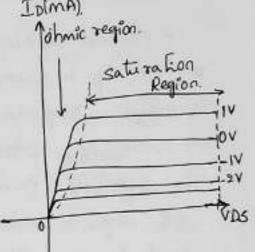

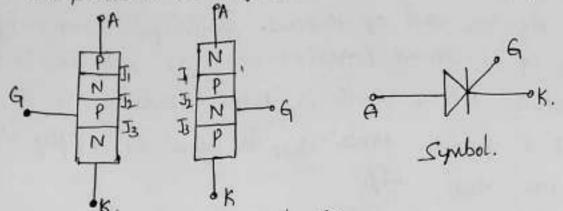

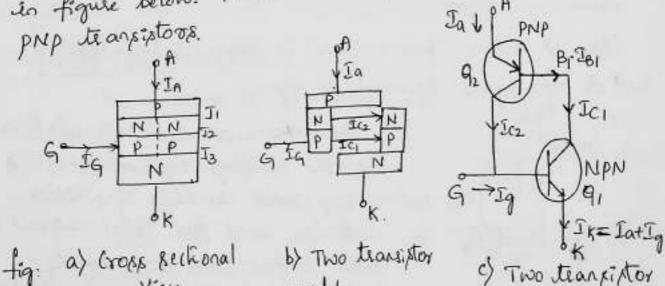

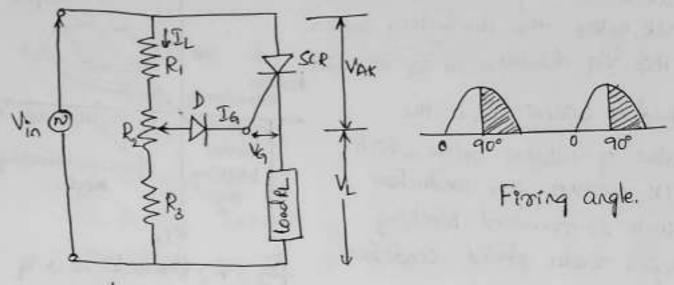

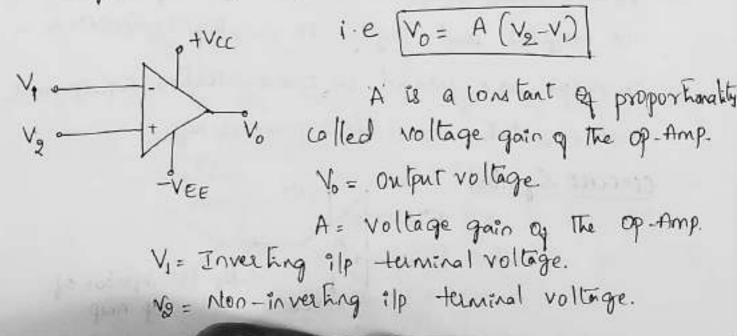

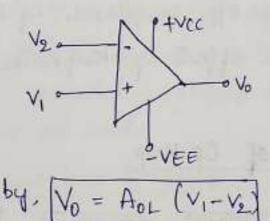

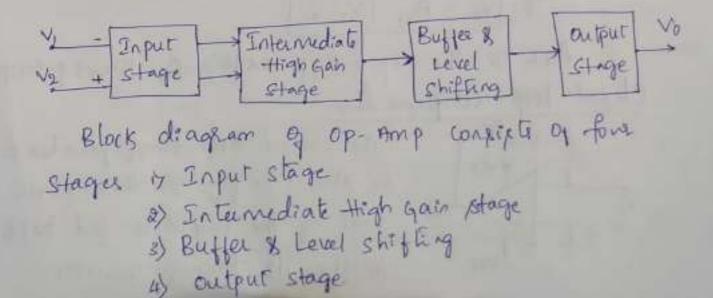

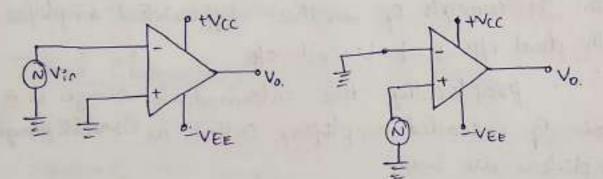

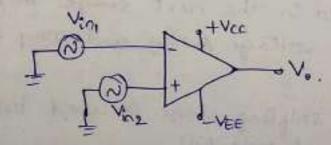

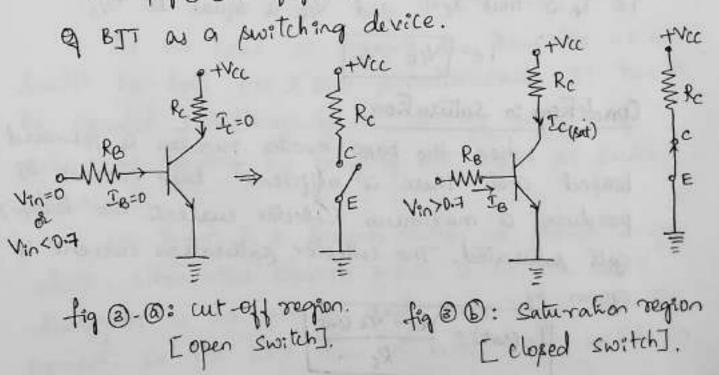

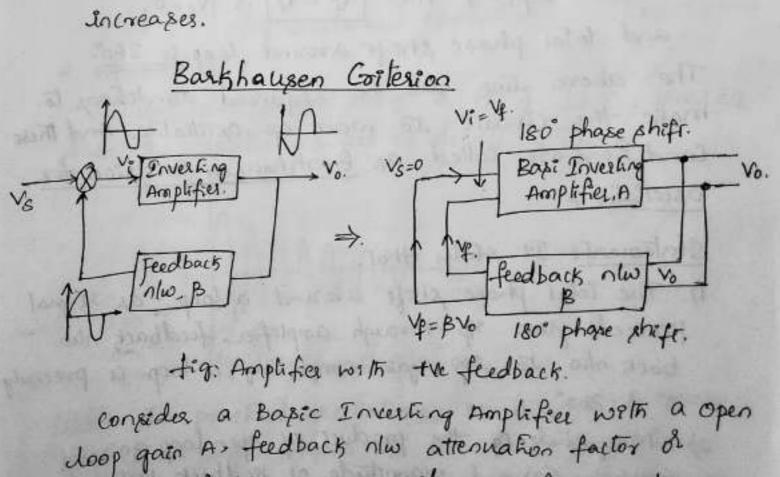

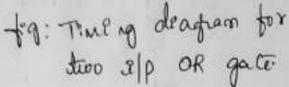

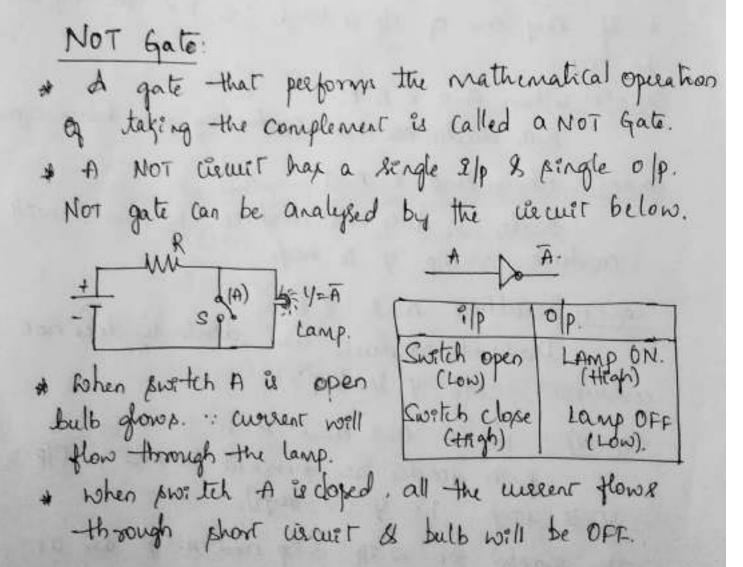

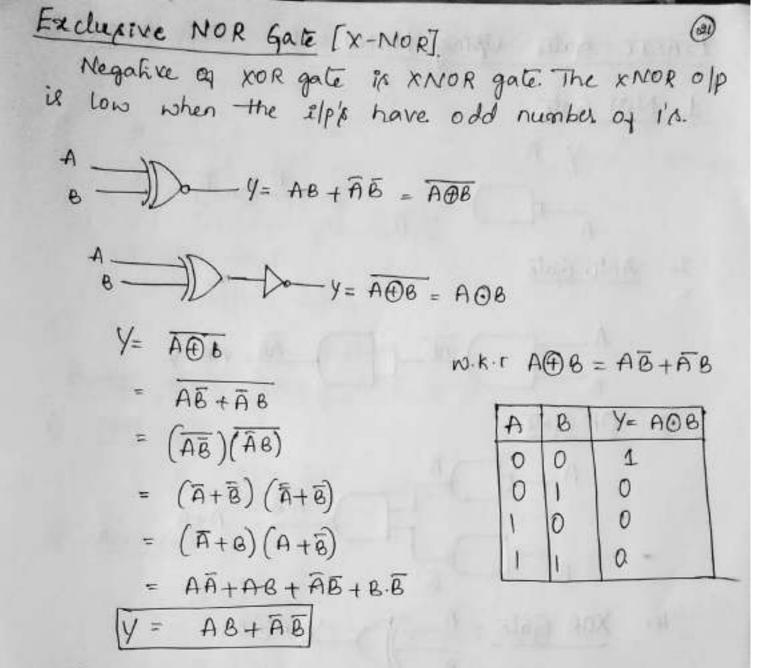

$N_{m} = \frac{1}{82} \times 100 \text{ f} \frac{50}{144.34 \text{ H}}$